# MU183020A 28G/32G bit/s PPG MU183021A 28G/32G bit/s 4ch PPG Operation Manual

# 23rd Edition

- For safety and warning information, please read this manual before attempting to use the equipment.

- Additional safety and warning information is provided in the MP1800A Signal Quality Analyzer Installation Guide and the MT1810A 4 Slot Chassis Installation Guide. Please also refer to them before using the equipment.

- Keep this manual with the equipment.

# **ANRITSU CORPORATION**

# Safety Symbols

To prevent the risk of personal injury or loss related to equipment malfunction, Anritsu Corporation uses the following safety symbols to indicate safety-related information. Ensure that you clearly understand the meanings of the symbols BEFORE using the equipment. Some or all of the following symbols may be used on all Anritsu equipment. In addition, there may be other labels attached to products that are not shown in the diagrams in this manual.

## Symbols used in manual

This indicates a very dangerous procedure that could result in serious injury or death if not performed properly.

WARNING This indicates a hazardous procedure that could result in serious injury or death if not performed properly.

This indicates a hazardous procedure or danger that could result in light-to-severe injury, or loss related to equipment malfunction, if proper precautions are not taken.

### Safety Symbols Used on Equipment and in Manual

The following safety symbols are used inside or on the equipment near operation locations to provide information about safety items and operation precautions. Ensure that you clearly understand the meanings of the symbols and take the necessary precautions BEFORE using the equipment.

This indicates a prohibited operation. The prohibited operation is indicated symbolically in or near the barred circle.

This indicates an obligatory safety precaution. The obligatory operation is indicated symbolically in or near the circle.

This indicates a warning or caution. The contents are indicated symbolically in or near the triangle.

This indicates a note. The contents are described in the box.

These indicate that the marked part should be recycled.

MU183020A 28G/32G bit/s PPG MU183021A 28G/32G bit/s 4ch PPG **Operation Manual**

20 July 2012 (First Edition) 10 March 2022 (23rd Edition)

Copyright © 2012-2022, ANRITSU CORPORATION.

All rights reserved. No part of this manual may be reproduced without the prior written permission of the publisher.

The operational instructions of this manual may be changed without prior notice. Printed in Japan

# **Equipment Certificate**

Anritsu Corporation certifies that this equipment was tested before shipment using calibrated measuring instruments with direct traceability to public testing organizations recognized by national research laboratories, including the National Institute of Advanced Industrial Science and Technology, and the National Institute of Information and Communications Technology, and was found to meet the published specifications.

# **Anritsu Warranty**

Anritsu Corporation will repair this equipment free-of-charge if a malfunction occurs within one year after shipment due to a manufacturing fault, and software bug fixes will be performed in accordance with the separate Software End-User License Agreement, provide, however, that Anritsu Corporation will deem this warranty void when:

- The fault is outside the scope of the warranty conditions separately described in the operation manual.

- The fault is due to mishandling, misuse, or unauthorized modification or repair of the equipment by the customer.

- The fault is due to severe usage clearly exceeding normal usage.

- The fault is due to improper or insufficient maintenance by the customer.

- The fault is due to natural disaster, including fire, wind or flood, earthquake, lightning strike, or volcanic ash, etc.

- The fault is due to damage caused by acts of destruction, including civil disturbance, riot, or war, etc.

- The fault is due to explosion, accident, or breakdown of any other machinery, facility, or plant, etc.

- The fault is due to use of non-specified peripheral or applied equipment or parts, or consumables, etc.

- The fault is due to use of a non-specified power supply or in a non-specified installation location.

- The fault is due to use in unusual environments<sup>(Note)</sup>.

- The fault is due to activities or ingress of living organisms, such as insects, spiders, fungus, pollen, or seeds.

In addition, this warranty is valid only for the original equipment purchaser. It is not transferable if the equipment is resold.

Anritsu Corporation shall assume no liability for damage or financial loss of the customer due to the use of or a failure to use this equipment, unless the damage or loss is caused due to Anritsu Corporation's intentional or gross negligence.

#### Note:

For the purpose of this Warranty, "unusual environments" means use:

- In places of direct sunlight

- In dusty places

- Outdoors

- In liquids, such as water, oil, or organic solvents, and medical fluids, or places where these liquids may adhere

- In salty air or in place chemically active gases (sulfur dioxide, hydrogen sulfide, chlorine, ammonia, nitrogen dioxide, or hydrogen chloride etc.) are present

- In places where high-intensity static electric charges or electromagnetic fields are present

- In places where abnormal power voltages (high or low) or instantaneous power failures occur

- In places where condensation occurs

- In the presence of lubricating oil mists

- In places at an altitude of more than 2,000 m

- In the presence of frequent vibration or mechanical shock, such as in cars, ships, or airplanes

# **Anritsu Corporation Contact**

In the event of this equipment malfunctions, please contact an Anritsu Service and Sales office. Contact information can be found on the last page of the printed version of this manual, and is available in a separate file on the PDF version.

# Notes On Export Management

This product and its manuals may require an Export License/Approval by the Government of the product's country of origin for re-export from your country.

Before re-exporting the product or manuals, please contact us to confirm whether they are export-controlled items or not.

When you dispose of export-controlled items, the products/manuals need to be broken/shredded so as not to be unlawfully used for military purpose.

# Software End-User License Agreement (EULA)

Please carefully read and accept this Software End-User License Agreement (hereafter this EULA) before using (includes executing, copying, installing, registering, etc.) this Software (includes programs, databases, scenarios, etc., used to operate, set, etc., Anritsu electronic equipment, etc.). By using this Software, you shall be deemed to have agreed to be bound by the terms of this EULA, and Anritsu Corporation (hereafter Anritsu) hereby grants you the right to use this Software with the Anritsu-specified equipment (hereafter Equipment) for the purposes set out in this EULA.

#### Article 1. Grant of License and Limitations

- 1. You may not sell, transfer, rent, lease, lend, disclose, sublicense, or otherwise distribute this Software to third parties, whether or not paid therefor.

- 2. You may make one copy of this Software for backup purposes only.

- 3. You are not permitted to reverse engineer, disassemble, decompile, modify or create derivative works of this Software.

- 4. This EULA allows you to install one copy of this Software on one piece of Equipment.

#### Article 2. Disclaimers

To the extent not prohibited by law, in no event shall Anritsu be liable for direct, or any incidental, special, indirect or consequential damages whatsoever, including, without limitation, damages for loss of profits, loss of data, business interruption or any other commercial damages or losses, and damages claimed by third parties, arising out of or related to your use or inability to use this Software, unless the damages are caused due to Anritsu's intentional or gross negligence.

#### Article 3. Limitation of Liability

If a fault (bug) is discovered in this Software, making this Software unable to operate as described in the operation manual or specifications even though you have used this Software as described in the manual, Anritsu shall at its own discretion, fix the bug, or replace the software, or suggest a workaround, free-of-charge, provided, however, that the faults caused by the following items and any of your lost or damaged data whatsoever shall be excluded from repair and the warranty.

- i) If this Software is deemed to be used for purposes not described in the operation manual or specifications.

- ii) If this Software has been used in conjunction with other non-Anritsu-approved software.

- iii) If this Software or the Equipment has been modified, repaired, or otherwise altered without Anritsu's prior approval.

- iv) For any other reasons out of Anritsu's direct control and responsibility, such as but not limited to, natural disasters, software virus infections, or any devices other than this Equipment, etc.

- 2. Expenses incurred for transport, hotel, daily allowance, etc., for on-site repairs or replacement by Anritsu engineers necessitated by the above faults shall be borne by you.

- 3. The warranty period for faults listed in Section 1 of this Article shall be either 6 months from the date of purchase of this Software or 30 days after the date of repair or replacement, whichever is longer.

#### Article 4. Export Restrictions

You shall not use or otherwise export or re-export directly or indirectly this Software except as authorized by the laws and regulations of Japan and the United States, etc. In particular, this Software shall not be exported or re-exported (a) into any Japan or US embargoed countries or (b) to anyone restricted by the Japanese export control regulations, or the US Treasury Department's list of Specially Designated Nationals or the US Department of Commerce Denied Persons List or Entity List. In using this Software, you warrant that you are not located in any such embargoed countries or on any such lists. You also agree that you will not use or otherwise export or re-export this Software for any purposes prohibited by the Japanese and US laws and regulations, including, without limitation, the development, design and manufacture or production of missiles or nuclear, chemical or biological weapons of mass destruction, and conventional weapons.

#### Article 5. Change of Terms

Anritsu may change without your approval the terms of this EULA if the changes are for the benefit of general customers, or are reasonable in light of the purpose of this EULA and circumstances of the changes. At the time of change, Anritsu will inform you of those changes and its effective date, as a general rule 45 days, in advance on its website, or in writing or by e-mail.

#### Article 6. Termination

Anritsu may terminate this EULA immediately if you violate any conditions described herein. This EULA shall also be terminated immediately by Anritsu if there is any good reason that it is deemed difficult to continue this EULA, such as your violation of Anritsu copyrights, patents, etc. or any laws and ordinances, or if it turns out that you belong to an antisocial organization or has a socially inappropriate relationship with members of such organization.

2. You and Anritsu may terminate this EULA by a written notice to the other party 30 days in advance.

#### Article 7. Damages

If Anritsu suffers any damages or loss, financial or otherwise, due to your violation of the terms of this EULA, Anritsu shall have the right to seek proportional damages from you.

Article 8. Responsibility after Termination Upon termination of this EULA in accordance with Article 6, you shall cease all uses of this Software immediately and shall as directed by Anritsu either destroy or return this Software and any backup copies, full or partial, to Anritsu.

### Article 9. Negotiation for Dispute Resolution

If matters of interpretational dispute or items not covered under this EULA arise, they shall be resolved by negotiations in good faith between you and Anritsu.

### Article 10. Governing Law and Court of Jurisdiction

This EULA shall be governed by and interpreted in accordance with the laws of Japan without regard to the principles of the conflict of laws thereof, and any disputes arising from or in relation to this EULA that cannot be resolved by negotiation described in Article 9 shall be subject to and be settled by the exclusive agreed jurisdiction of the Tokyo District Court of Japan.

#### **Revision History:**

February 29th, 2020 December 17th, 2021

# **CE Conformity Marking**

Anritsu affixes the CE Conformity marking on the following product in accordance with the Decision 768/2008/EC to indicate that it conforms to the EMC, LVD and RoHS directive of the European Union (EU).

### **CE marking**

( (

#### 1. Product Model

Plug-in Units:

MU183020A 28G/32G bit/s PPG

### 2. Applied Directive and Standards

When the MU183020A 28G/32G bit/s PPG is installed in the MP1900A, the applied directive and standards of this unit conform to those of the MP1900A main frame.

PS: About main frame

Please contact Anritsu for the latest information on the main frame types that MU183020A can be used with.

# **UKCA Marking**

Anritsu affixes the UKCA marking on the following product in accordance with the guidance to indicate that it conforms to the EMC, LVD, and RoHS regulations in the United Kingdom.

### **UKCA** marking

#### 1. Product Model

Model:

MU183020A 28G/32G bit/s PPG

### 2. Applied Regulations and Standards

When the MU183020A 28G/32G bit/s PPG is installed in the MP1900A, the applied regulations and standards of this unit conform to those of the MP1900A main frame.

PS: About main frame

Please contact Anritsu for the latest information on the main frame types that MU183020A can be used with.

# **RCM Conformity Marking**

Anritsu affixes the RCM mark on the following products in accordance with the regulation to indicate that they conform to the EMC framework of Australia/New Zealand.

### **RCM** marking

#### 1. Product Model

Plug-in Units:

MU183020A 28G/32G bit/s PPG MU183021A 28G/32G bit/s 4ch PPG

#### 2. Applied Standards

When the MU183020A 28G/32G Gbit/s PPG or MU183021A 28G/32G bit/s 4ch PPG is installed in the MP1800A or MT1810A, the applied directive and standards of this unit conform to those of the MP1800A or MT1810A main frame.

PS: About main frame

Please contact Anritsu for the latest information on the main frame types that MU183020A/MU183021A can be used with.

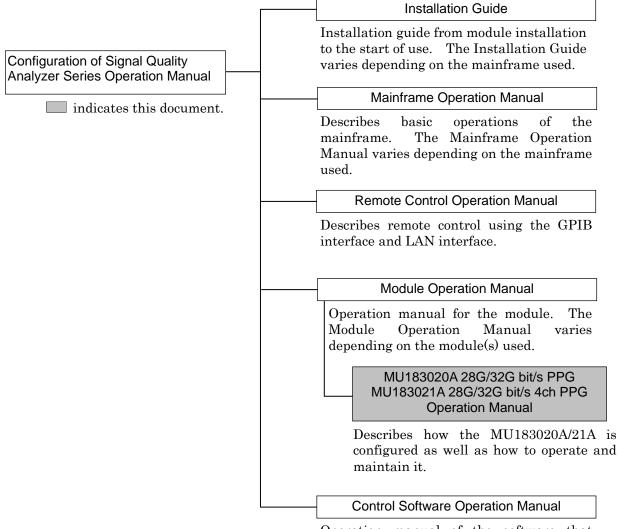

# **About This Manual**

A testing system combining an MP1800A Signal Quality Analyzer or MT1810A 4-Slot Chassis mainframe, module(s), and control software is called a Signal Quality Analyzer Series. The operation manuals of the Signal Quality Analyzer Series consist of separate documents for the installation guide, the mainframe, remote control operation, module(s), and control software, as shown below.

Operation manual of the software that controls the Signal Quality Analyzer Series.

# **Table of Contents**

| Chapte   | r 1 Overview        |     |

|----------|---------------------|-----|

| -<br>1.1 | Product Overview    |     |

| 1.2      | Product Composition |     |

| 1.3      | Specifications      | 1-7 |

|          |                     |     |

| Chapte   | r 2 Before Use      |     |

| 2.1 | Installation to Signal Quality Analyzer2-2 |

|-----|--------------------------------------------|

| 2.2 | How to Operate Application2-2              |

| 2.3 | Preventing Damage2-3                       |

# Chapter 3 Panel Layout and Connectors ...... 3-1

| 3.1 | Panel Layout            | 3-2 |

|-----|-------------------------|-----|

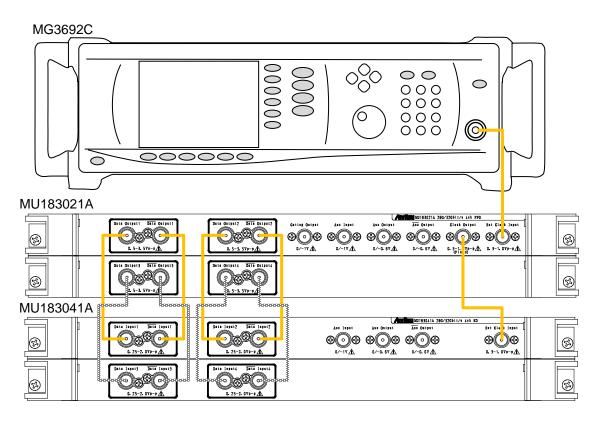

| 3.2 | Inter-Module Connection | 3-4 |

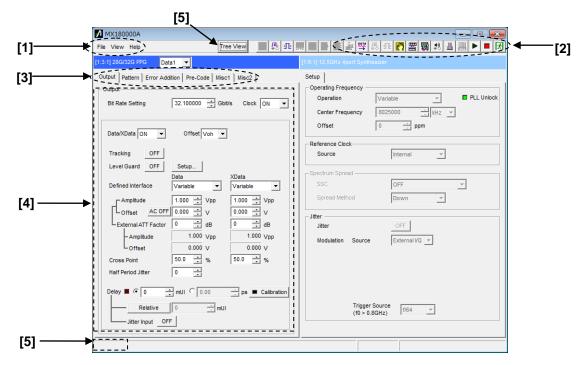

# Chapter 4 Configuration of Screens and Tabs 4-1

| 4.1 | Configuration of Entire Setup Dialog Box | 4-2 |

|-----|------------------------------------------|-----|

| 4.2 | Operation Tab Windows                    | 4-3 |

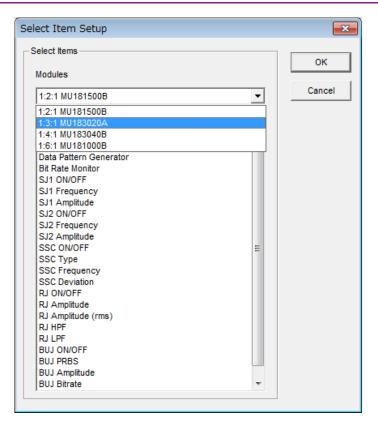

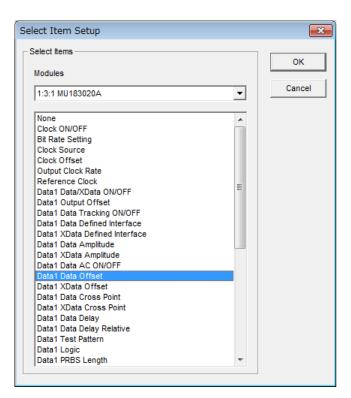

| 4.3 | User Customize Dialog                    | 4-4 |

# Chapter 5 Operation Method ......5-1

| 5.1 | Setting Output Interface              |      |

|-----|---------------------------------------|------|

| 5.2 | Setting Test Patterns                 | 5-13 |

| 5.3 | Adding Errors                         | 5-40 |

| 5.4 | Setting Pre-Code Function             | 5-43 |

| 5.5 | Misc1 Function                        | 5-45 |

| 5.6 | Misc2 Function                        | 5-56 |

| 5.7 | Inter-module Synchronization Function | 5-77 |

| 5.8 | Multi Channel Calibration Function    | 5-78 |

| 5.9 | Unit Sync Function                    |      |

|     |                                       |      |

| Chapter | 6 Usage Examples                     | 6-1 |

|---------|--------------------------------------|-----|

| 6.1     | Measuring Optical Transceiver Module | 6-2 |

## Chapter 7 Remote Command ......7-1

# Chapter 8 Performance Test ...... 8-1

# Chapter 9 Maintenance......9-1

| 9.1 | Daily Maintenance   | 9-2 |

|-----|---------------------|-----|

| 9.2 | Cautions on Storage | 9-2 |

| 9.3 | Transportation      | 9-3 |

| 9.4 | Calibration         | 9-4 |

| 9.5 | Disposal            | 9-4 |

### Chapter 10 Troubleshooting ...... 10-1

| 10.1 | Problems Discovered during Module Replacement 10-2 |  |  |  |

|------|----------------------------------------------------|--|--|--|

| 10.2 | Problems Discovered during Output Waveform         |  |  |  |

|      | Observation10-2                                    |  |  |  |

| 10.3 | Problems Discovered during Error Rate              |  |  |  |

|      | Measurement 10-3                                   |  |  |  |

| Appendix A Pseudo-Random PatternA-1                         |

|-------------------------------------------------------------|

| Appendix B List of Initial SettingsB-1                      |

| Appendix C Setting RestrictionsC-1                          |

| Appendix D Performance Test Record Sheet .D-1               |

| Appendix E Preparing to Use Unit Sync<br>FunctionE-1        |

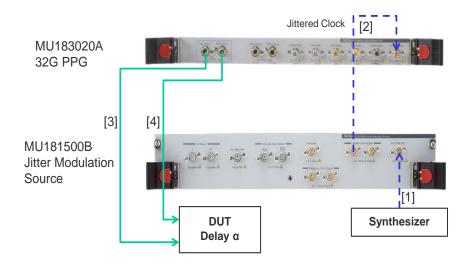

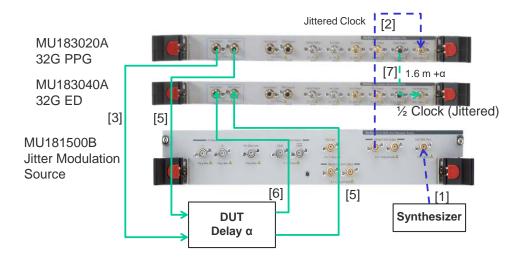

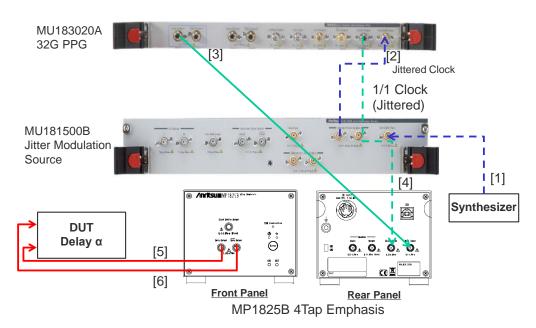

| Appendix F Connection Examples for Jitter<br>MeasurementF-1 |

| Appendix G How to Use PAM Function G-1                      |

This chapter provides an overview of the MU183020A 28G/32G bit/s PPG and the MU183021A 28G/32G bit/s 4ch PPG (hereinafter, referred to as "MU183020A/MU183021A").

This document only explains the MU183020A, unless there is a special item.

| 1.1 | Product Overview1-2 |                                   |  |

|-----|---------------------|-----------------------------------|--|

| 1.2 | Produc              | ct Composition1-3                 |  |

|     | 1.2.1               | Standard configuration1-3         |  |

|     | 1.2.2               | Options1-4                        |  |

|     | 1.2.3               | Application parts 1-6             |  |

| 1.3 | Specif              | ications1-7                       |  |

|     | 1.3.1               | Specifications for MU183020A 1-7  |  |

|     | 1.3.2               | Specifications for MU183021A 1-19 |  |

|     |                     |                                   |  |

# **1.1 Product Overview**

The MU183020A/MU183021A is a plug-in module that can be built into a Signal Quality Analyzer mainframe.

It can generate a variety of patterns within the operating frequency range, including PRBS, DATA, Zero-Substitution, and Mixed patterns.

Various option configurations are available for the MU183020A/MU183021A. This module is therefore useful for research, development, and production of various types of digital communication equipment, modules, and devices.

The features of these modules are listed below:

- Capable of generating PRBS, DATA, Zero-Substitution, and Mixed patterns.

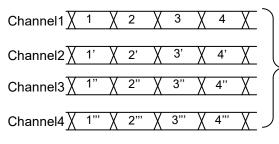

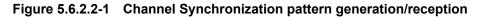

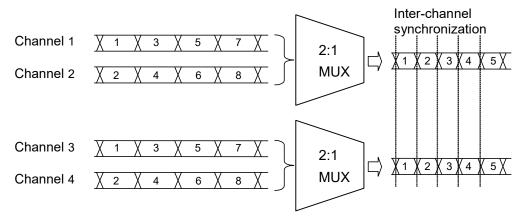

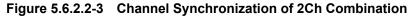

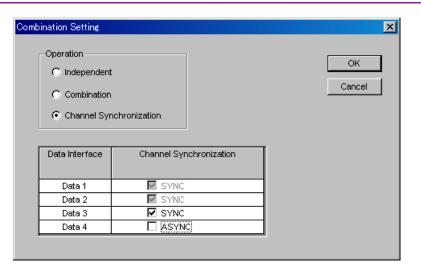

- Capable of outputting while synchronizing multiple-channel signal bits. (Channel Synchronization)

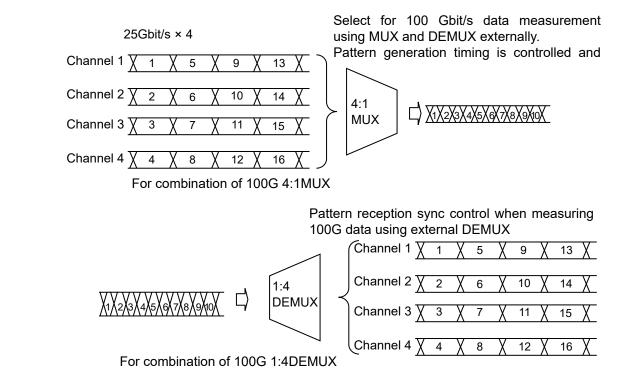

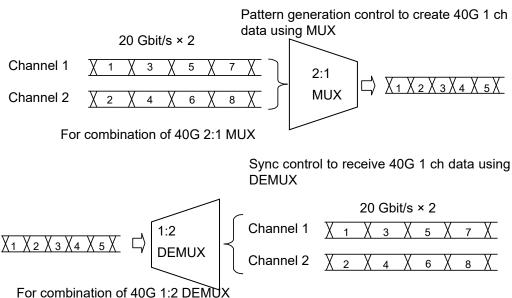

- For MU183020A-x22/x23 and MU183021A, Channel Combination between channels in a module can be performed. This enables the generation of multiplexing signal by using Multiplexer (MUX) and De-multiplexer (DEMUX).

- Wide range of output level from 0.5 to 3.5 Vp-p (Option x13/x23)

# **1.2 Product Composition**

# 1.2.1 Standard configuration

Table 1.2.1-1 and Table 1.2.1-2 show the standard compositions of the MU183020A/MU183021A.

| ltem        | Model name/symbol | Product name                      | Q'ty | Remarks                                |

|-------------|-------------------|-----------------------------------|------|----------------------------------------|

| Mainframe   | MU183020A         | 28G/32G bit/s PPG                 | 1    |                                        |

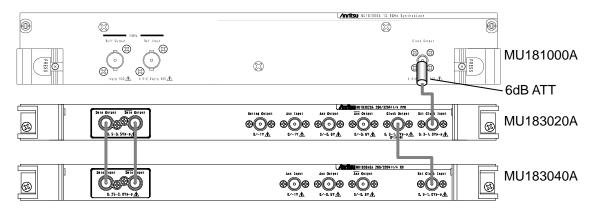

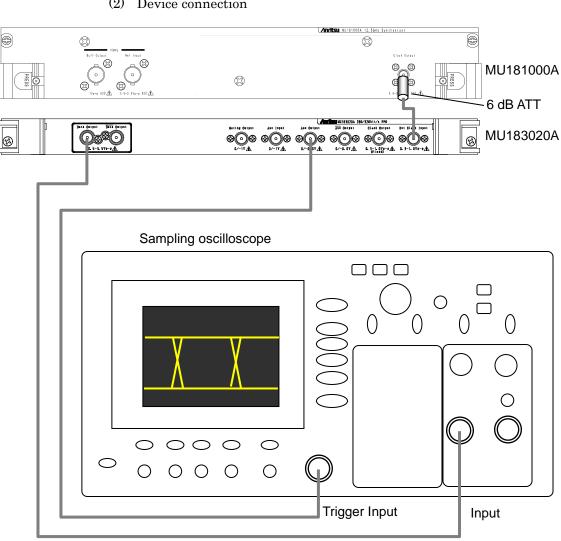

| Accessories | J0541E            | 6 dB Fixed Attenuator             | 1    |                                        |

|             | J1137             | Terminator                        | 3    | Clock Output,<br>Aux Output $\times 2$ |

|             | J1359A            | Coaxial Adaptor (K-P.K-J,<br>SMA) | 1    | Clock Output                           |

|             | J1341A            | Open                              | 1    | Ext Clock Input                        |

|             | Z0897A            | MP1800A Manual CD                 | 1    | CD-ROM                                 |

|             | Z0918A            | MX180000A Software CD             | 1    | CD-ROM                                 |

### Table 1.2.1-2 Standard composition of MU183021A

| ltem        | Model name/symbol | Product name                      | Q'ty | Remarks                         |

|-------------|-------------------|-----------------------------------|------|---------------------------------|

| Mainframe   | MU183021A         | 28G/32G bit/s 4ch PPG             | 1    |                                 |

| Accessories | J0541E            | 6 dB Fixed Attenuator             | 1    |                                 |

|             | J1137             | Terminator                        | 3    | Clock Output,<br>Aux Output × 2 |

|             | J1359A            | Coaxial Adaptor (K-P.K-J,<br>SMA) | 1    | Clock Output                    |

|             | J1341A            | Open                              | 1    | Ext Clock Input                 |

|             | Z0897A            | MP1800A Manual CD                 | 1    | CD-ROM                          |

|             | Z0918A            | MX180000A Software CD             | 1    | CD-ROM                          |

# 1.2.2 Options

Table 1.2.2-1 and Table 1.2.2-2 show the options for the MU183020A/MU183021A. Table 1.2.2-3, Table 1.2.2-4 and Table 1.2.2-5 show the application parts for option. All options are sold separately.

| Model name    | Product name          | Remarks |

|---------------|-----------------------|---------|

| MU183020A-x01 | 32G bit/s Extension   |         |

| MU183020A-x12 | 1ch 2 V Data Output   | *1      |

| MU183020A-x13 | 1ch 3.5 V Data Output | *1      |

| MU183020A-x22 | 2ch 2 V Data Output   | *1      |

| MU183020A-x23 | 2ch 3.5 V Data Output | *1      |

| MU183020A-x30 | 1ch Data Delay        | *2      |

| MU183020A-x31 | 2ch Data Delay        | *3      |

| Table 1.2.2-1 | Options of MU183020A |

|---------------|----------------------|

|---------------|----------------------|

\*1: Select one from among them.

\*2: The MU183020A-x12/x13 is required.

\*3: The MU183020A-x22/x23 is required.

| Table 1.2.2-2 | Options of MU183021A |

|---------------|----------------------|

|---------------|----------------------|

| Model name    | Product name          | Remarks |

|---------------|-----------------------|---------|

| MU183021A-x01 | 32G bit/s Extension   |         |

| MU183021A-x12 | 4ch 2 V Data Output   | *       |

| MU183021A-x13 | 4ch 3.5 V Data Output | *       |

| MU183021A-x30 | 4ch Data Delay        |         |

\*: Select either of them.

#### Note:

.

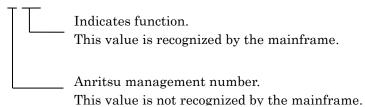

Option name format is as follows:

MU183020A-x x x

### 1.2 Product Composition

| Model name/symbol | Product name                   | Q'ty | Remarks         |

|-------------------|--------------------------------|------|-----------------|

| J1137             | Terminator                     | 2    | Data Output × 2 |

| J1359A            | Coaxial Adaptor (K-P.K-J, SMA) | 2    | Data Output × 2 |

#### Table 1.2.2-3 Standard accessories for MU183020A-x12/x13

#### Table 1.2.2-4Standard accessories for MU183020A-x22/x23

| Model name/symbol | Product name                   | Q'ty | Remarks         |

|-------------------|--------------------------------|------|-----------------|

| J1137             | Terminator                     | 4    | Data Output × 4 |

| J1359A            | Coaxial Adaptor (K-P.K-J, SMA) | 4    | Data Output × 4 |

#### Table 1.2.2-5 Standard accessories for MU183021A-x12/x13

| Model name/symbol | Product name                   | Q'ty | Remarks         |

|-------------------|--------------------------------|------|-----------------|

| J1137             | Terminator                     | 8    | Data Output × 8 |

| J1359A            | Coaxial Adaptor (K-P.K-J, SMA) | 8    | Data Output × 8 |

# 1.2.3 Application parts

Table 1.2.3-1 shows the application parts for the MU183020A/MU183021A. All application parts are sold separately.

| Model name/<br>symbol | Product name                                                  | Remarks                                                                                         |

|-----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| J1449A                | Measurement kit                                               | Coaxial cable<br>(K connector ) 0.8 m × 2<br>Coaxial cable 0.8 m × 2<br>Coaxial cable 1.0 m × 1 |

| J1625A                | Coaxial cable 1 m                                             | SMA connector                                                                                   |

| J1342A                | Coaxial cable 0.8 m                                           | APC3.5 connector                                                                                |

| J1439A                | Coaxial cable (0.8 m, K connector)                            | K connector                                                                                     |

| J1137                 | Terminator                                                    |                                                                                                 |

| J1359A                | Coaxial Adaptor (K-P.K-J, SMA)                                |                                                                                                 |

| 41KC-3                | Precision Fixed Attenuator 3 dB                               |                                                                                                 |

| 41KC-6                | Precision Fixed Attenuator 6 dB                               |                                                                                                 |

| 41KC-10               | Precision Fixed Attenuator 10 dB                              |                                                                                                 |

| 41KC-20               | Precision Fixed Attenuator 20 dB                              |                                                                                                 |

| K240C                 | Precision Power Divider                                       |                                                                                                 |

| J1349A                | Coaxial Cable 0.3 m                                           | APC3.5 connector                                                                                |

| J1550A                | Coaxial skew match cable (0.8 m, APC3.5 connector)            | Pair cable                                                                                      |

| J1551A                | Coaxial skew match cable (0.8 m, K connector)                 | Pair cable                                                                                      |

| J1611A                | Coaxial cable (1.3 m, K connector)                            | K connector                                                                                     |

| J1741A                | Fixed Electrical Length Coaxial Cable (0.8 m,<br>K Connector) | K connector                                                                                     |

| J1615A*               | Coaxial Cable set (Jitter-PPG-Emphasis)                       | Cable set for jitter tolerance<br>measurement                                                   |

| J1618A*               | Coaxial Cable set (Jitter-2chPPG-Emphasis)                    | Cable set for jitter tolerance<br>measurement                                                   |

| J1620A                | Coaxial Cable (0.9 m K Connector)                             | K connector                                                                                     |

| W3594AE               | MU183020A/MU183021A Operation manual                          | Printed version, English                                                                        |

| W3594AW               | MU183020A/MU183021A Operation manual                          | Printed version, Japanese                                                                       |

| Z0306A                | Wrist strap                                                   |                                                                                                 |

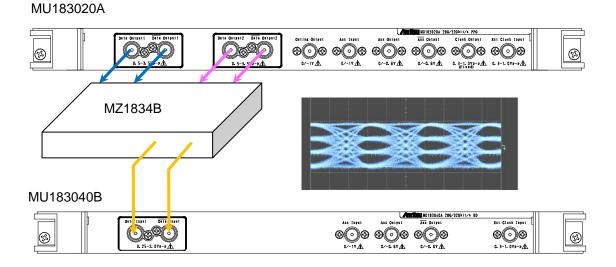

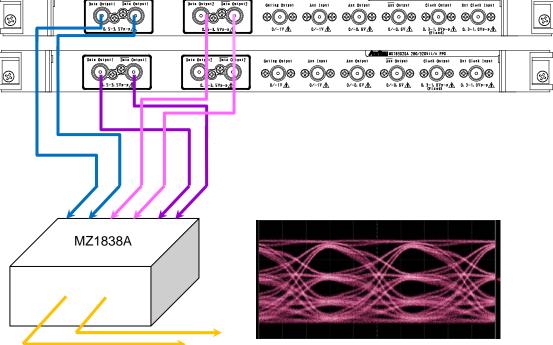

| MZ1834A               | 4PAM Converter                                                |                                                                                                 |

| MZ1838A               | 8PAM Converter                                                |                                                                                                 |

| J1678A                | ESD Protection Adapter-K                                      | K connector                                                                                     |

| Table 1.2.3-1 | Application Parts |

|---------------|-------------------|

|---------------|-------------------|

\*: For examples of how to connect instruments with coaxial cables, refer to Appendix F.

# **1.3 Specifications**

# 1.3.1 Specifications for MU183020A

Table 1.3.1-1 Operating Bit Rate

| ltem                                  | Specifications                                                                         |

|---------------------------------------|----------------------------------------------------------------------------------------|

| MU181000A/B synchronized operation ON | This item can be specified when MU181000A or MU181000B are installed to the same unit. |

| When the Output Clock                 |                                                                                        |

| Rate is set to Full Rate              |                                                                                        |

| Setting Range                         | 2.400 000 to 12.500 000 Gbit/s / 0.000 001 Gbit/s step                                 |

|                                       | 12.500 002 to 20.000 000 Gbit/s / 0.000 002 Gbit/s step                                |

|                                       | 20.000 002 to 25.000 000 Gbit/s / 0.000 002 Gbit/s step                                |

|                                       | 25.000 004 to 28.100 000 Gbit/s / 0.000 004 Gbit/s step*1                              |

|                                       | 25.000 004 to 32.100 000 Gbit/s / 0.000 004 Gbit/s step*2                              |

| Offset                                | -1000 to +1000 ppm / 1 ppm step*3                                                      |

| When the Output Clock                 |                                                                                        |

| Rate is set to Half Rate              |                                                                                        |

| Setting Range                         | 2.400 000 to 25.000 000 Gbit/s / 0.000 002 Gbit/s step                                 |

|                                       | 25.000 004 to 28.100 000 Gbit/s / 0.000 004 Gbit/s step*1                              |

|                                       | 25.000 004 to 32.100 000 Gbit/s / 0.000 004 Gbit/s step*2                              |

| Offset                                | -1000 to +1000 ppm / 1 ppm step*3                                                      |

|                                       | *1: Not available Option x01                                                           |

|                                       | -                                                                                      |

|                                       | *2: Available Option x01                                                               |

|                                       | *3: The setting range varies depending on the bit rate setting.                        |

|                                       | At following bit rate setting, setting range is from $-1000$ to 0 ppm.                 |

|                                       | Full rate: 12.500000 Gbit/s, 25.000000 Gbit/s                                          |

| Half rate: | 25.000000 Gbit/s |  |

|------------|------------------|--|

|                                                                                             |                                                                                                                        | ,                                                      |                                                        |  |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

| Item                                                                                        |                                                                                                                        | Specifications                                         |                                                        |  |

| MU181500B synchronized<br>operation ON<br>When the Output Clock<br>Rate is set to Full Rate | This item can be specif<br>MU181500B are instal                                                                        | fied when MU181000A,<br>led to the same unit.          | MU181000B and                                          |  |

| Setting Range                                                                               | 2.400 000 to 3.125 00                                                                                                  | 0 Gbit/s / 0.000 001 Gbi                               | t/s step                                               |  |

|                                                                                             |                                                                                                                        | 0 Gbit/s / 0.000 001 Gbi                               | -                                                      |  |

|                                                                                             | 6.400 001 to 12.500 0                                                                                                  | 00 Gbit/s / 0.000 001 Gb                               | oit/s step                                             |  |

|                                                                                             | 12.800 002 to 15.000 0                                                                                                 | 00 Gbit/s / 0.000 002 Gł                               | oit/s step                                             |  |

|                                                                                             | 15.000 002 to 20.000 000 Gbit/s / 0.000 002 Gbit/s step                                                                |                                                        |                                                        |  |

|                                                                                             | 20.000 002 to 25.000 000 Gbit/s / 0.000 002 Gbit/s step                                                                |                                                        |                                                        |  |

|                                                                                             | 25.600 004 to 28.100 000 Gbit/s / 0.000 004 Gbit/s step*1<br>25.600 004 to 32.100 000 Gbit/s / 0.000 004 Gbit/s step*2 |                                                        |                                                        |  |

|                                                                                             |                                                                                                                        |                                                        | oit/s step*2                                           |  |

| Offset<br>When the Output Clock<br>Rate is set to Half Rate                                 | -1000 to +1000 ppm / 1 ppm step*3                                                                                      |                                                        |                                                        |  |

| Setting Range                                                                               | 2.400 000 to 3.125 000                                                                                                 | 0 Gbit/s / 0.000 002 Gbi                               | t/s step                                               |  |

|                                                                                             |                                                                                                                        | 0 Gbit/s / 0.000 002 Gbi                               | -                                                      |  |

|                                                                                             | 6.400 002 to 12.500 0                                                                                                  | 6.400 002 to 12.500 000 Gbit/s / 0.000 002 Gbit/s step |                                                        |  |

|                                                                                             | $12.800\;002$ to $25.000\;000$ Gbit/s / $0.000\;002$ Gbit/s step                                                       |                                                        |                                                        |  |

|                                                                                             | 25.600 004 to 28.100 0                                                                                                 | 00 Gbit/s / 0.000 004 Gb                               | oit/s step*1                                           |  |

|                                                                                             |                                                                                                                        | 00 Gbit/s / 0.000 004 Gł                               | oit/s step*2                                           |  |

| Offset                                                                                      | -1000 to +1000 ppm / 1                                                                                                 | l ppm step*3                                           |                                                        |  |

| External Clock                                                                              |                                                                                                                        |                                                        |                                                        |  |

| When the Output Clock<br>Rate is set to Full Rate                                           | Operating bit rate range                                                                                               | Input Clock<br>Frequency                               | Relationship<br>Between Bitrate and<br>Clock Frequency |  |

|                                                                                             | 2.4 to 16.0 Gbit/s                                                                                                     | 2.4 to 16.0 Gbit/s                                     | Operate at 1/1 clock                                   |  |

|                                                                                             | 16.0 to 20.4 Gbit/s                                                                                                    | 8.0 to 10.2 Gbit/s                                     | Operate at 1/2 clock                                   |  |

|                                                                                             | 20.0 to 28.1 Gbit/s*1                                                                                                  | 10.0 to 14.05 Gbit/s                                   | Operate at 1/2 clock                                   |  |

|                                                                                             | 20.0 to 32.1 Gbit/s*2                                                                                                  | 10.0 to 16.05 Gbit/s                                   | Operate at 1/2 clock                                   |  |

|                                                                                             | 25.0 to 28.1 Gbit/s*1                                                                                                  | 6.25 to 7.025 GHz                                      | Operate at 1/4 clock                                   |  |

|                                                                                             | 25.0 to 32.1 Gbit/s*2                                                                                                  | 6.25 to 8.025 Gbit/s                                   | Operate at 1/4 clock                                   |  |

| When the Output Clock<br>Rate is set to Half Rate                                           | <b></b>                                                                                                                |                                                        |                                                        |  |

|                                                                                             | Operating bit rate<br>range                                                                                            | Input Clock<br>Frequency                               | Relationship<br>Between Bitrate and<br>Clock Frequency |  |

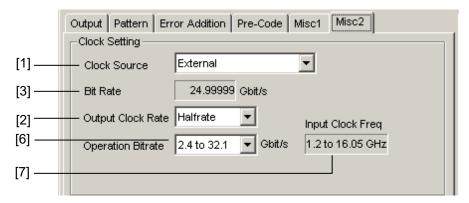

|                                                                                             | 2.4 to 28.1 Gbit/s*1                                                                                                   | 1.2 to 14.05 Gbit/s                                    | Operate at 1/2 clock                                   |  |

|                                                                                             | 2.4 to 32.1 Gbit/s*2                                                                                                   | 1.2 to 16.05 Gbit/s                                    | Operate at 1/2 clock                                   |  |

|                                                                                             | 25.0 to 28.1 Gbit/s*1                                                                                                  | 6.25 to 7.025 GHz                                      | Operate at 1/4 clock                                   |  |

|                                                                                             | 25.0 to 32.1 Gbit/s* <sup>2</sup>                                                                                      | 6.25 to 8.025 Gbit/s                                   | Operate at 1/4 clock                                   |  |

| Table 1 3 1-1 | <b>Operating Bit Rate</b> | (Cont'd) |

|---------------|---------------------------|----------|

|               | Operating Dit Nate        |          |

| Item                                              | Specifications           |                          |                                                        |

|---------------------------------------------------|--------------------------|--------------------------|--------------------------------------------------------|

| Tracking with external clock<br>MU181500B         |                          |                          |                                                        |

| When the Output Clock                             |                          |                          |                                                        |

| Rate is set to Full Rate                          | Operating bit rate range | Input Clock<br>Frequency | Relationship<br>Between Bitrate and<br>Clock Frequency |

|                                                   | 2.4 to 15.0 Gbit/s       | 2.4 to 15.0 Gbit/s       | Operate at 1/1 clock                                   |

|                                                   | 12.5 to 20.0 Gbit/s      | 6.25 to 10.0 Gbit/s      | Operate at 1/2 clock                                   |

|                                                   | 20.0 to 28.1 Gbit/s*1    | 10.0 to 14.05 Gbit/s     | Operate at 1/2 clock                                   |

|                                                   | 20.0 to 30.0 Gbit/s*2    | 10.0 to 16.05 Gbit/s     | Operate at 1/2 clock                                   |

|                                                   | 25.0 to 32.1 Gbit/s*2    | 6.25 to 8.025 Gbit/s     | Operate at 1/4 clock                                   |

| When the Output Clock<br>Rate is set to Half Rate |                          |                          |                                                        |

|                                                   | Operating bit rate range | Input Clock<br>Frequency | Relationship<br>Between Bitrate and<br>Clock Frequency |

|                                                   | 2.4 to 28.1 Gbit/s*1     | 1.2 to 14.05 Gbit/s      | Operate at 1/2 clock                                   |

|                                                   | 2.4 to 30.0 Gbit/s*2     | 1.2 to 15.0 Gbit/s       | Operate at 1/2 clock                                   |

|                                                   | 30.0 to 32.1 Gbit/s*2    | 7.5 to 8.025 Gbit/s      | Operate at 1/4 clock                                   |

| Table 1.3.1-1 | Operating Bit Rate (Cont'd) |

|---------------|-----------------------------|

|---------------|-----------------------------|

| Table 1.3.1-2 | External Clock Input |

|---------------|----------------------|

|---------------|----------------------|

| ltem                  | Specifications                     |

|-----------------------|------------------------------------|

| Number of Input       | 1 (Single-Ended)                   |

| Input frequency range | 1.2 to 16.05 GHz                   |

| Input amplitude       | 0.3 to 1.0 Vp-p (-6.5 to +4.0 dBm) |

| Termination           | ΑC/50 Ω                            |

| Connector             | SMA connector (f.)                 |

| Item                | Specifications                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aux Input           |                                                                                                                                                              |

| Number of Input     | 1 (Single-Ended)                                                                                                                                             |

| Signal Type         | Error Injection, Burst                                                                                                                                       |

| Minimum Pulse Width | 1/128 of data rate                                                                                                                                           |

| Input level         | 0/-1 V (H: -0.25 to 0.05 V / L: -1.1 to -0.8 V)                                                                                                              |

| Termination         | $GND/50 \ \Omega$                                                                                                                                            |

| Connector           | SMA connector (f.)                                                                                                                                           |

| Aux Output          |                                                                                                                                                              |

| Number of Output    | 2 (Differential output)                                                                                                                                      |

| Signal Type         | 1/n Clock (n=4, 6, 8, 10510, 512), Pattern Sync, Burst Out2, OFF                                                                                             |

| Pattern Sync        |                                                                                                                                                              |

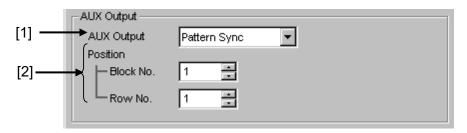

| PRBS, PRGM          | Position: 1 to {(Least common multiple of Pattern Length' and 128)<br>-135}, in 8 steps                                                                      |

| Mixed Data          | When the pattern length is 511 bits or less, Pattern Length' is the length as an integer multiple so that it becomes 512 bits or more.<br>Block No. setting: |

| Mixeu Data          | 1 to the Block No. specified for Mixed Data, in single steps                                                                                                 |

|                     | Row No. setting:                                                                                                                                             |

|                     | 1 to the Row No. specified for Mixed Data, in single steps                                                                                                   |

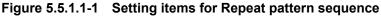

| Burst Out2          | i to the new ite, specifica for mixed Data, in single steps                                                                                                  |

| Burst Trigger Delay | 0 to (Burst Cycle – 128) bits / 8 bits step                                                                                                                  |

| Pulse Width         | 0 to (Burst Cycle – 128) bits / 8 bits step                                                                                                                  |

| Output level        | 0/-0.6 V (H: -0.25 to 0.05 V / L: -0.80 to -0.45 V)                                                                                                          |

| Terminator          | GND/50 $\Omega$                                                                                                                                              |

| Connector           | SMA connector (f.)                                                                                                                                           |

| Table 1.3.1-3 Aux Input and Output |

|------------------------------------|

|------------------------------------|

| ltem                | Specifications                                                                                                                         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Burst               | Burst Output                                                                                                                           |  |  |

| Burst Trigger Delay | 0 to (Burst Cycle $-128$ ) bits / 8 bits step                                                                                          |  |  |

| Pulse Width         | 0 to (Burst Cycle $-128$ ) bits / 8 bits step                                                                                          |  |  |

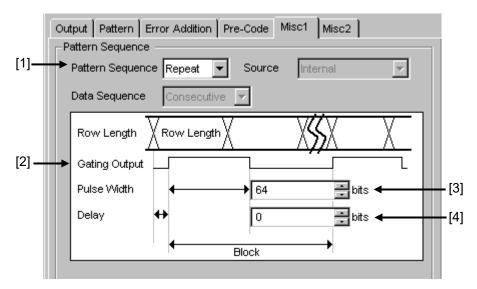

| Repeat              | Timing Signal Output                                                                                                                   |  |  |

| Timing Signal Cycle | INT (Pattern Length / $128$ ) × $128$ (other than Mixed)                                                                               |  |  |

| Timing Signal Pulse | For PRBS, Zero-Substitution, Data:                                                                                                     |  |  |

| Width               | 0 to {(Least common multiple of Pattern Length' and 128) –128}, in 8-bit steps                                                         |  |  |

|                     | The maximum settable number is 34 359 738 240.                                                                                         |  |  |

|                     | When the pattern length is 511 bits or less, Pattern Length' is the length as an integer multiple so that it becomes 512 bits or more. |  |  |

|                     | For Mixed:                                                                                                                             |  |  |

|                     | 0 to (Row length $\times$ Number of rows $\times$ Number of blocks –128), in 8-bit steps                                               |  |  |

|                     | The maximum settable number is 2 415 918 976.                                                                                          |  |  |

| Timing Signal Delay | Same value as the timing signal pulse width.                                                                                           |  |  |

| Output control      | ON/OFF switching                                                                                                                       |  |  |

| Output level        | 0/-1  V (H: -0.25  to  0.05  V / L: -1.25  to  -0.8  V)                                                                                |  |  |

| Terminator          | $GND/50 \ \Omega$                                                                                                                      |  |  |

| Connector           | SMA connector (f.)                                                                                                                     |  |  |

Table 1.3.1-4 Gating output

| Item                                | Specifications                                                                      |

|-------------------------------------|-------------------------------------------------------------------------------------|

| PRBS                                |                                                                                     |

| Pattern Length                      | $2^{n}-1$ ( n = 7, 9, 10, 11, 15, 20, 23, 31)                                       |

| Mark ratio                          | 1/2 (1/2INV is supported by a logical inversion.)                                   |

| Zero-Substitution                   |                                                                                     |

| Additional bit                      | 0 bit, 1 bit                                                                        |

| Pattern Length                      | $2^{n}$ (n = 7, 9, 10, 11, 15, 20, 23)                                              |

|                                     | $2^{n}-1$ (n = 7, 9, 10, 11, 15, 20, 23)                                            |

| Start position                      | Substitutes the bit coming after the maximum "0" successive bits.                   |

| Length of Consecutive               | 1 to (Pattern Length–1) bits                                                        |

| Zero Bits                           | If the bit coming after Zero-substitution is "0", then it is replaced with "1".     |

| Data                                |                                                                                     |

| Data Length                         | 2 to 268 435 456 bits / 1 bit step                                                  |

| Mixed Pattern                       |                                                                                     |

| Pattern                             | Data                                                                                |

| Mixed Block                         | To the smaller of the following values:                                             |

|                                     | 1 to 511 Block / 1 Block step                                                       |

|                                     | $INT\left(\frac{268435456}{ROW \text{ count}} \times \text{Data length} ight)$ bits |

|                                     | $INT\left(\frac{2415919104}{ROW length} \times ROW count\right)$ bits               |

| Mixed Row Length                    | 1 536 to 2 415 919 104 / 256 bits step (Data + PRBS Length)                         |

| Data Length                         | 1 024 to 268 435 456 bits / 1 bit step                                              |

| Number of rows                      | 1 to 16 / 1 step                                                                    |

| Number of blocks                    | 1 to 511 / 1 step                                                                   |

| PRBS Pattern Length /<br>Mark ratio | Same as PRBS.                                                                       |

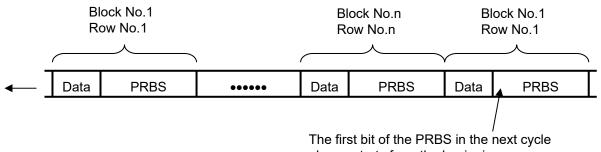

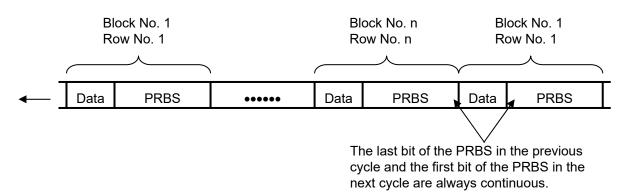

| PRBS Sequence                       | Restart, Consecutive                                                                |

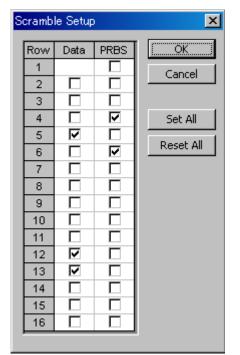

| Scramble                            | Can be set per PRBS and Data for each Block (except the Data area for Block 1)      |

#### Table 1.3.1-5 Generated pattern

### Table 1.3.1-6 Pattern Sequence

| ltem          | Specifications                                                      |        |

|---------------|---------------------------------------------------------------------|--------|

| Sequence      | Repeat/Burst                                                        |        |

| Repeat        | Continuous Pattern                                                  |        |

| Burst         |                                                                     |        |

| Source        | Internal, External-Trigger (Aux Input), External-Enable (Aux Input) |        |

| Data Sequence | Restart, Consecutive, Continuous                                    |        |

| Burst Cycle   | 1 536 to 2 147 483 648 bits / 256 bits step                         |        |

| Enable period | Internal: 1 024 to 2 147 483 392 bits / 256 bits                    | s step |

|               | Ext Trigger, Enable: 1 024 to 2 147 483 648 bits / 256 bits         | s step |

### Table 1.3.1-7 Pre-Code

| ltem            | Specifications                    |

|-----------------|-----------------------------------|

| ON/OFF          | Sets Pre-Code function ON and OFF |

| Modulation type | 2ch Combination: DQPSK            |

| Initial Data    | Choose 0 or 1.                    |

#### Table 1.3.1-8 Error addition

| Item             | Specifications                                                      |

|------------------|---------------------------------------------------------------------|

| Area             | ALL, Specific Block (Can be selected only for Mixed.)               |

| Internal trigger |                                                                     |

| Error Variation  | Repeat, Single                                                      |

| Error Ratio      | $A \times 10^{-b}$ (a=1 to 9, b=3 to 12)*                           |

| Insertion CH     | 1 to 32, or channel scan (Only when Internal is set.)               |

| External trigger |                                                                     |

| Control Method   | External-Trigger (Rise edge trigger), External-Disable (L: Disable) |

\*: Upper limit is 5E–3.

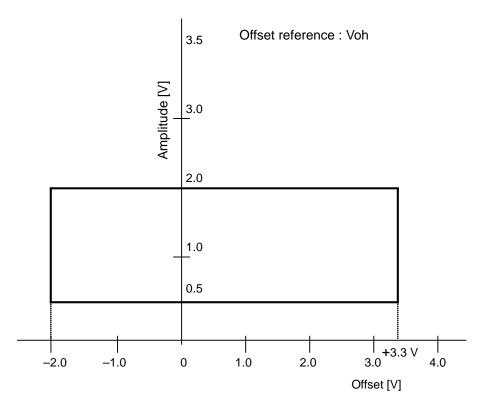

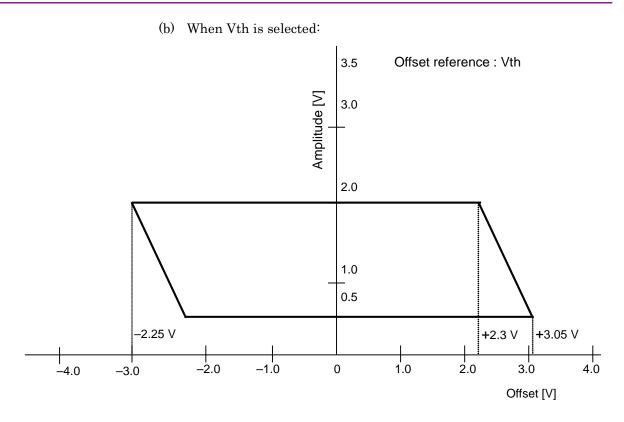

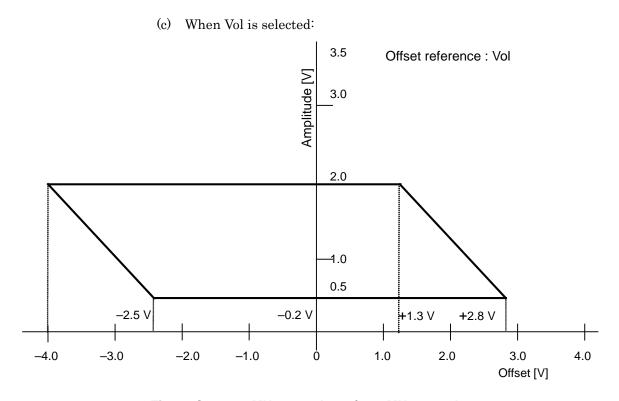

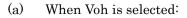

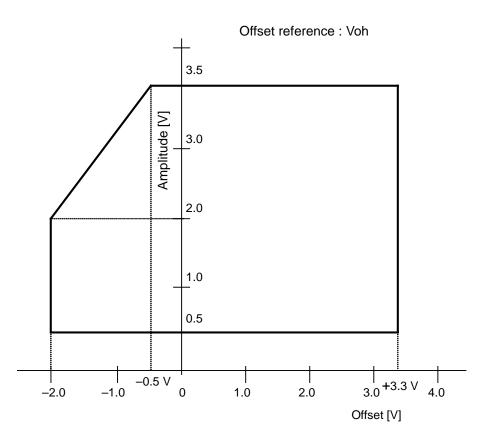

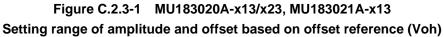

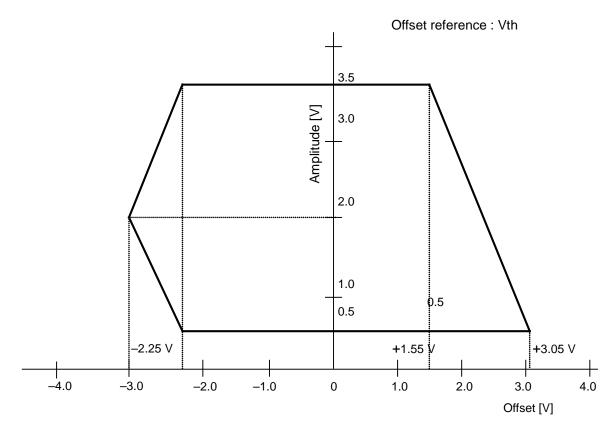

| Item                | Specifications*1                                                                       |

|---------------------|----------------------------------------------------------------------------------------|

| Number of outputs   | Option x12/x13:2 (Data, XData (Independent))                                           |

|                     | Option x22/x23:4 (Data1, XData1, Data2, XData2 (Independent))                          |

| Output amplitude    |                                                                                        |

| Setting range       | Option x12/x22: 0.5 to 2.0 Vp-p / 2 mV step                                            |

|                     | Option x13/x23: 0.5 to 3.5 Vp-p / 2 mV step                                            |

| Setting error       | $\pm 50 \text{ mV} \pm (17\% \text{ of set Amplitude})^{*2}$                           |

| Offset              |                                                                                        |

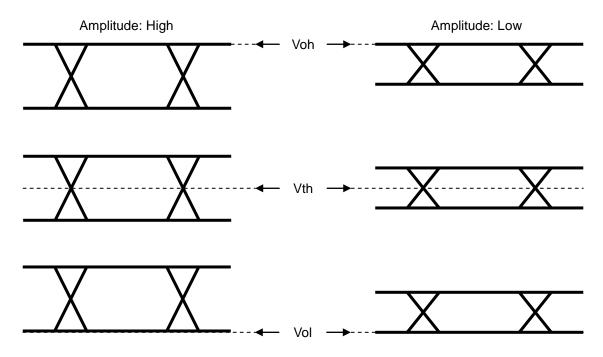

| Reference level     | Voh, Vth, Vol                                                                          |

| Setting range       | Voh: -2.0 to +3.3 V / 1 mV step                                                        |

|                     | Minimum value Vol: -4.0 V                                                              |

| Setting error       | $\pm 65 \text{ mV} \pm 10\%$ of offset (Vth) $\pm$ (Output amplitude setting error/ 2) |

| Current limitation  | Sourcing 50 mA                                                                         |

|                     | Sinking 80 mA                                                                          |

| Defined Interface   | NECL, SCFL, NCML, PCML, LVPECL                                                         |

| Cross Point         |                                                                                        |

| Setting range       | 20 to 80% / 0.1% step (Amplitude: 1.0 to 2.0 Vp-p for option x12/x22)                  |

|                     | (Amplitude: 1.0 to 3.5 Vp-p for option x13/x23)                                        |

|                     | 30 to 70% / 0.1% step (Amplitude: 0.5 to 0.998 Vp-p)                                   |

| Rising/falling time | $12 \text{ ps} (20 \text{ to } 80\%)^{*3,*4,*5}$                                       |

| Half Period Jitter  | -20 to 20 / 1 step                                                                     |

| Table ' | 1.3.1-9 | Data | Output |

|---------|---------|------|--------|

|---------|---------|------|--------|

\*1: Unless otherwise specified, these are defined with the conditions of PRBS2<sup>31</sup>-1, Mark ratio 1/2, and Cross Point 50%.

These values are monitored using an applicable part (J1439A coaxial cable, 0.8 m, K connector) at a sampling oscilloscope bandwidth of 70 GHz.

\*2: Under the following conditions:

| Option x01    | Bit Rate                                    | Cross Point |

|---------------|---------------------------------------------|-------------|

| Not available | 25 Gbit/s and 28.1 Gbit/s                   | 30 to 80%   |

|               | Full range except 25 Gbit/s and 28.1 Gbit/s | 50%         |

| Available     | 25 Gbit/s and 32.1 Gbit/s                   | 30 to 80%   |

|               | Full range except 25 Gbit/s and 32.1 Gbit/s | 50%         |

\*3: If Option x01 is not available, then this is at 28.1 Gbit/s.

If Option x01 is available, then this is at 32.1 Gbit/s.

\*4: Amplitude: 2.0 Vp-p for option x12/x22

Amplitude: 3.5 Vp-p for option x13/x23

\*5: Typical value

| Item                            | Specifications*1                                  |  |

|---------------------------------|---------------------------------------------------|--|

| Jitter                          | Jitter (p-p): 8 ps p- $p^{*3,*4,*5,*6}$           |  |

|                                 | Jitter (RMS): 700 fs*3,*4, *5,*6                  |  |

|                                 | Intrinsic RJ (RMS): 300 fs*3,*4,*5,*6,*8          |  |

| Waveform Distortion<br>(0-peak) | $\pm 25 \text{ mV} \pm 15\%^{*3,*4,*5}$           |  |

| Output control                  | ON/OFF switching                                  |  |

| Skew between channels*7         | $\pm 0.25 \text{ UI}^{*9}$                        |  |

| Termination                     | AC/DC switching, 50 $\Omega$                      |  |

|                                 | For DC: GND, -2 V, +1.3 V, +3.3 V, Open           |  |

| Connector                       | K (f.)                                            |  |

| Data/XData Tracking             | This can be performed by operation on the screen. |  |

| Level Guard                     | Amplitude, Voh, and Vol can be specified.         |  |

| External ATT factor             | 0 to 40 dB / 1 dB step                            |  |

Table 1.3.1-9 Data Output (Cont'd)

\*6: Using oscilloscope with residual jitter of less than 200 fs (RMS).

- \*7: When Option x22 or Option x23 is available.

- \*8: Defined with a repetition pattern of "1" and "0"

- \*9: When Option x31 is available.

| ltem             | Specifications*1                                      |

|------------------|-------------------------------------------------------|

| Frequency        |                                                       |

| Full Rate        | $2.4 \text{ to } 28.1 \text{ GHz}^{*2}$               |

|                  | $2.4 \text{ to } 32.1 \text{ GHz}^{*3}$               |

|                  | Operation bit rate is same as clock output frequency. |

| Half Rate        | $1.2 \text{ to } 14.05 \text{ GHz}^{*2}$              |

|                  | $1.2 \text{ to } 16.05 \text{ GHz}^{*3}$              |

|                  | Operation bit rate is half of clock output frequency. |

| Number of Output | 1                                                     |

| Amplitude        | 0.3 to 1.0 Vp-p                                       |

| Output control   | ON/OFF switching                                      |

| Termination      | ΑC/50 Ω                                               |

| Connector        | K (f.)                                                |

\*1: These values are monitored using an applicable part (J1439A coaxial cable, 0.8 m, K connector) at a sampling oscilloscope bandwidth of 70 GHz.

- \*2: Option x01 not available.

- \*3: Option x01 available.

| ltem                  | Specifications                                                                         |

|-----------------------|----------------------------------------------------------------------------------------|

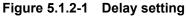

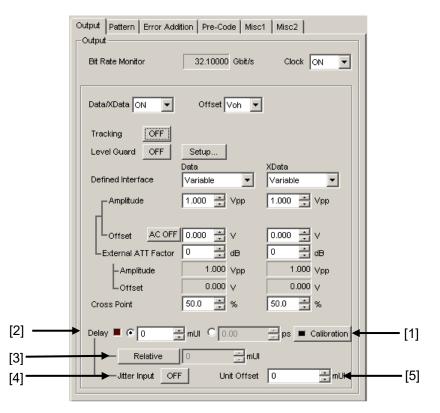

| Phase Setting Range   | –1 000 to +1 000 mUI / 2 mUI step                                                      |

| Accuracy              | ±50 mUIp-p*2,*3,*4                                                                     |

|                       | ±75 mUIp-p* <sup>2,*3,*5</sup>                                                         |

| mUI - ps switching    | Available                                                                              |

| Calibration           | Available                                                                              |

| Calibration indicator | This indicator is on when Calibration is required due to:                              |

|                       | •Change in 1/1 Clock frequency by ±250 kHz.                                            |

|                       | • Change in the ambient temperature by $\pm 5$ degree.                                 |

|                       | *1: When Option x30 or Option x31 is available.                                        |

|                       | *2: When using an item with an oscilloscope residual jitter of less than 200 fs (RMS). |

|                       | *3: Typical value                                                                      |

|                       | *4: Bit rate $\leq 28.1$ Gbit/s                                                        |

|                       | *5: Bit rate > 28.1 Gbit/s                                                             |

Table 1.3.1-11 Data Delay\*1

| Item                                | Specifications                                                                                                 |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| Jitter tolerance mask* <sup>3</sup> | Bit rate: 16 Gbit/s, 28.1 Gbit/s*1                                                                             |  |

|                                     | 16 Gbit/s, 28.1 Gbit/s, 32.1 Gbit/s* <sup>2</sup>                                                              |  |

|                                     | Pattern: PRBS2 <sup>31</sup> –1                                                                                |  |

|                                     | Temperature: 20 to 30°C                                                                                        |  |

|                                     | SSC with a 5300 ppm amplitude and RJ of 0.3 UI can be simultaneously applied by using MU181500B.               |  |

|                                     | These specifications are defined assuming the following conditions:<br>Loopback connection with MU183040A/41A. |  |

|                                     | G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G<br>G                                             |  |

Table 1.3.1-12

Jitter tolerance

- \*1: Option x01 not available.

- \*2: Option x01 available.

- \*3: The tolerance will be extended in Version 7.09.00 or any later version of MX180000A.

| ltem                                  | Specifications                                                                              |  |

|---------------------------------------|---------------------------------------------------------------------------------------------|--|

| Combination Setting <sup>*1, *2</sup> |                                                                                             |  |

| 2ch Combination                       | Alternately outputs each bit in pattern as 56/64 Gbit/s band signal source to two channels. |  |

| Channel Synchronization <sup>*1</sup> |                                                                                             |  |

| Number of channels                    | $2 \text{ to } 4^{*_3}$                                                                     |  |

| Output                                |                                                                                             |  |

| Phase Setting Range                   | -64 000 to +64 000 mUI*4                                                                    |  |

| Phase setting step                    | 2 mUI *4                                                                                    |  |

| Pattern                               |                                                                                             |  |

| Data                                  |                                                                                             |  |

| Data Length                           | 4 to 536 870 912 bits / 2 bits step*5                                                       |  |

| Mixed                                 |                                                                                             |  |

| Row Length                            | $3\ 072$ to $4\ 831\ 838\ 208\ /\ 512$ bits step* <sup>5</sup>                              |  |

| Data Length                           | 2 048 to 536 870 912 bits / 2 bits step*5                                                   |  |

| Burst                                 |                                                                                             |  |

| Burst Cycle                           | $3\ 072$ to $4\ 294\ 967\ 296$ bits / $512$ bits step* <sup>5</sup>                         |  |

| Enable period                         | Internal: 2 048 to 4 294 966 784 bits / 512 bits step*5                                     |  |

|                                       | Ext Trigger, Enable: 2 048 to 4 294 967 296 bits / 512 bits step*5                          |  |

| Delay                                 | 0 to (Burst Cycle $-128$ ) $\times$ 2 bits / 16 bits step <sup>*5</sup>                     |  |

| Pulse Width                           | 0 to (Burst Cycle – 128) × 2 bits / 16 bits step* <sup>5</sup>                              |  |

| Gating Output Repeat<br>(Data)        |                                                                                             |  |

| Pulse Width                           | 0 to 68 719 476 480 / 16 bits step*5                                                        |  |

| Delay                                 | 0 to 68 719 476 480 / 16 bits step*5                                                        |  |

| Repeat (Mixed)                        |                                                                                             |  |

| Pulse Width                           | 0 to 4 831 837 952 / 16 bits step*5                                                         |  |

| Delay                                 | 0 to 4 831 837 952 / 16 bits step*5                                                         |  |

|                                       | *1: Option x31 is required for target channels.                                             |  |

|                                       | *2: Combination extending over multiple slots cannot be set.                                |  |

|                                       |                                                                                             |  |

|                                       | *3: When target channels are installed successively from Slot 1.                            |  |

Table 1.3.1-13 Multichannel operation

\*5: Common to every channel specified by Combination Setting.

\*4: A separate value can be set for each channel. This value is common to both Channel Combination and Channel Synchronization.

| ltem                         | Specifications                                          |

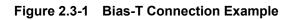

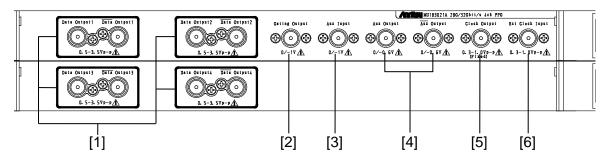

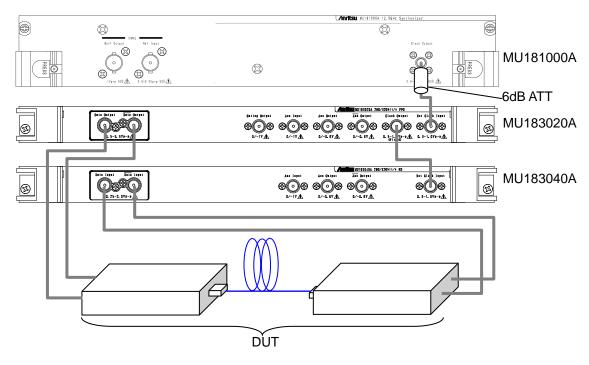

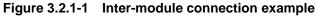

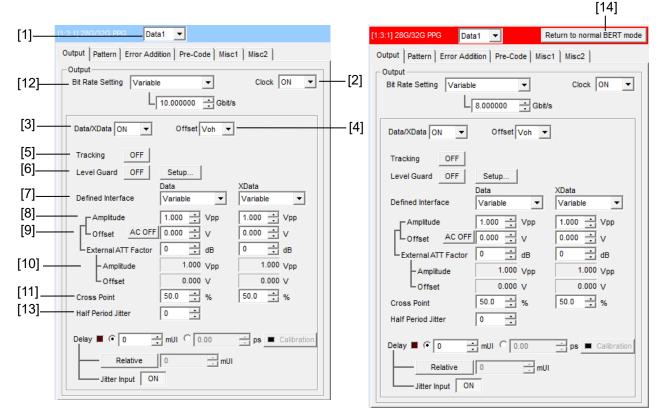

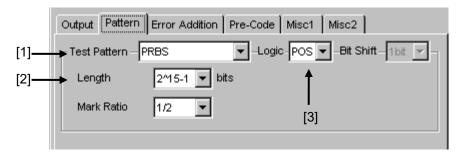

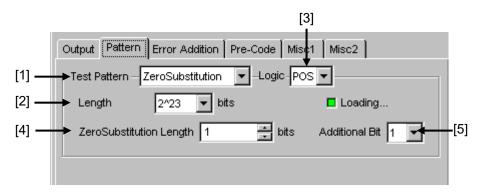

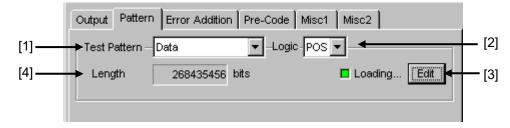

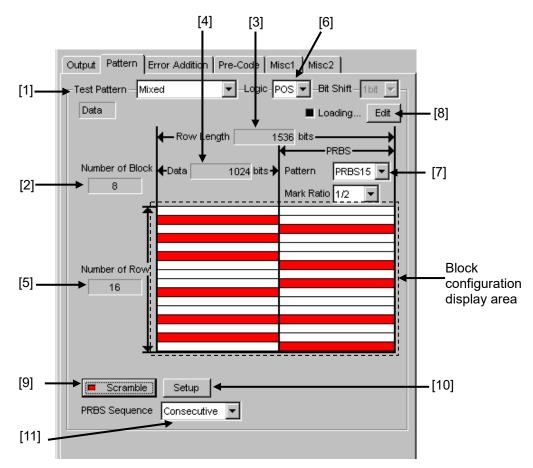

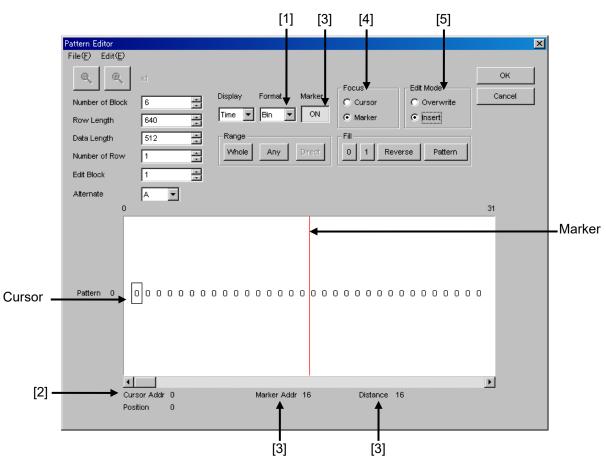

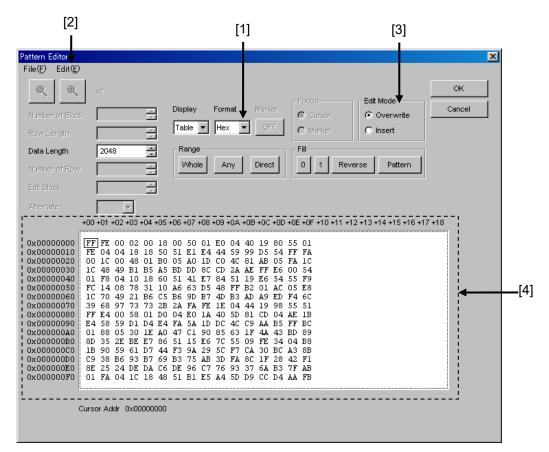

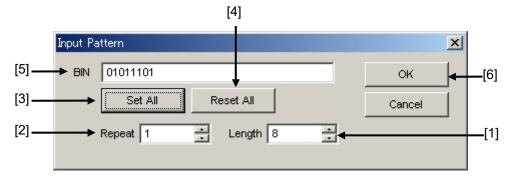

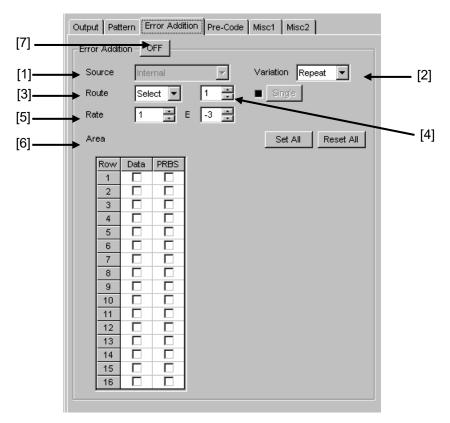

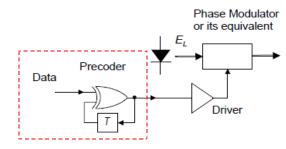

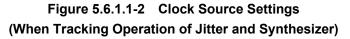

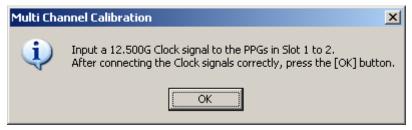

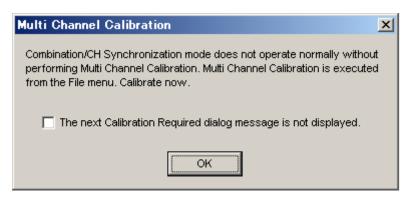

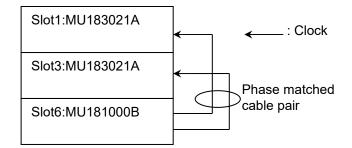

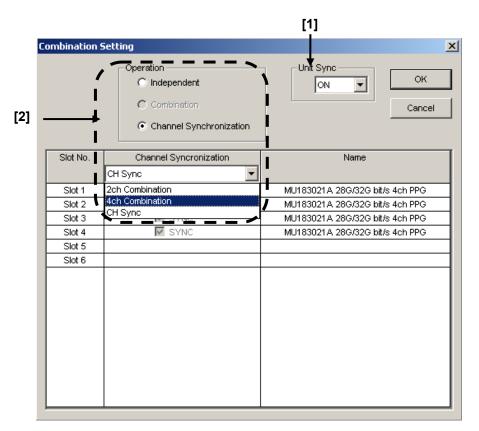

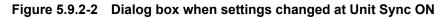

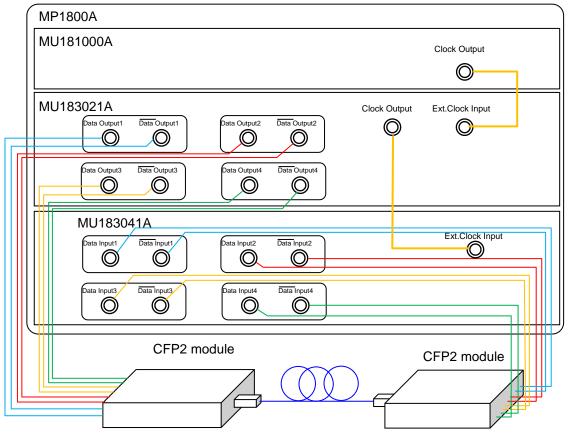

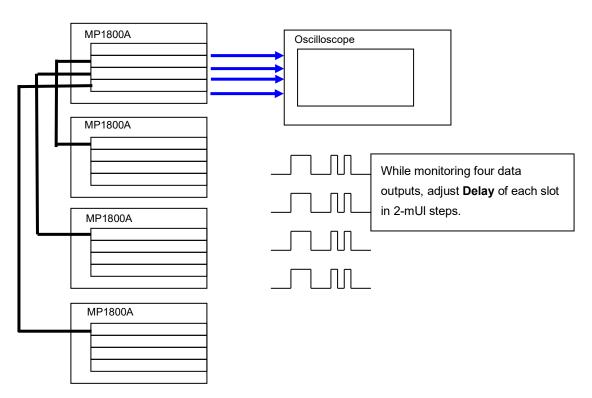

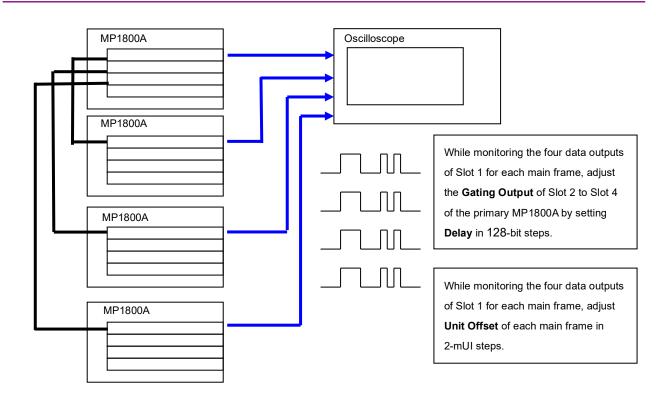

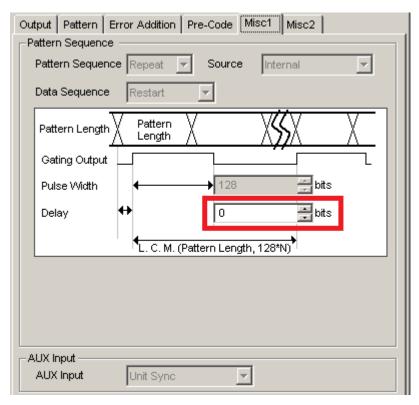

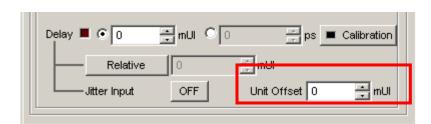

|------------------------------|---------------------------------------------------------|