### MODEL 56100A SCALAR NETWORK ANALYZER

### **MAINTENANCE MANUAL**

### WARRANTY

The ANRITSU product(s) listed on the title page is (are) warranted against defects in materials and workmanship for one year from the date of shipment.

ANRITSU's obligation covers repairing or replacing products which prove to be defective during the warranty period. Buyers shall prepay transportation charges for equipment returned to ANRITSU for warranty repairs. Obligation is limited to the original purchaser. ANRITSU is not liable for consequential damages.

### LIMITATION OF WARRANTY

The foregoing warranty does not apply to ANRITSU connectors that have failed due to normal wear. Also, the warranty does not apply to defects resulting from improper or inadequate maintenance by the Buyer, unauthorized modification or misuse, or operation outside of the environmental specifications of the product. No other warranty is expressed or implied, and the remedies provided herein are the Buyer's sole and exclusive remedies.

### TRADEMARK ACKNOWLEDGEMENTS

V Connector and K Connector are registered trademarks of ANRITSU Company.

GPC-7 is a registered trademark of Amphenol Corporation.

ANACAT is a registered trademark of EEsof, Inc.

Ink Jet and Think Jet are registered trademarks of Hewlett-Packard Co.

MS-DOS is a registered trademark of Microsoft Corporation.

### NOTICE

ANRITSU Company has prepared this manual for use by ANRITSU Company personnel and customers as a guide for the proper installation, operation and maintenance of ANRITSU Company equipment and computer programs. The drawings, specifications, and information contained herein are the property of ANRITSU Company, and any unauthorized use or disclosure of these drawings, specifications, and information is prohibited; they shall not be reproduced, copied, or used in whole or in part as the basis for manufacture or sale of the equipment or software programs without the prior written consent of ANRITSU Company.

### **DECLARATION OF CONFORMITY**

Manufacturer's Name: ANRITSU COMPANY

Manufacturer's Address: Microwave Measurements Division

490 Jarvis Drive

Morgan Hill, CA 95037-2809

USA

declares that the product specified below:

**Product Name:**

Scalar Network Analyzers

**Model Number:**

56100A

conforms to the requirement of:

EMC Directive 89/336/EEC as amended by Council Directive 92/31/EEC & 93/68/EEC Low Voltage Directive 73/23/EEC as amended by Council directive 93/68/EEC

### **Electromagnetic Interference:**

Emissions: CISPR 11:1990/EN55011:1991 Group 1 Class A

Immunity: IEC 1000-4-2:1995/prEN50082-1:1995 - 4kV CD, 8kV AD

IEC 1000-4-3:1993/ENV50140:1994 - 3V/m

IEC 1000-4-4:1995/prEN50082-1:1995 - 0.5kV SL, 1kV PL IEC 1000-4-5:1995/prEN50082-1:1995 - 0.5kV - 1kV LN 0.5kV - 1kV NG

0.5kV - 1kV GL

### **Electrical Safety Requirement:**

Product Safety: IEC 1010-1:1990 + A1/EN61010-1:1993

Morgan Hill, CA

5-SEPT-97

Date

European Contact: For Anritsu product EMC & LVD information, contact Anritsu LTD, Rutherford Close, Stevenage Herts, SG1 2EF UK, (FAX 44-1438-740202)

### Table Of Contents

#### Chapter 1 — General Information

Contains a general description of the ANRITSU Series 56100A Scalar Network Analyzer, product identification numbers, related manuals, accessories, and options. SWR Autotesters and detectors used with these systems are described along with precautions for use of these accessories. A list of recommended test equipment is provided.

#### Chapter 2 — Performance Verification

Provides two procedures for verifying signal channel accuracy, the only test necessary to ensure that the 56100A provides proper performance. These two procedures provide alternative methods for checking signal channel accuracy.

### Chapter 3 — Adjustments

This chapter contains the adjustment procedures for the Model 56100A. A performance verification test, using the DC Voltage Method, is also included at the end of paragraph 3-3. These procedures are usually used when out-of-specification conditions are noted during the Performance Verification tests of Chapter 2, or as a result of subassembly/component repair or replacement.

#### Chapter 4 - Troubleshooting

This chapter provides troubleshooting information for the 56100A Scalar Network Analyzer.

### **Chapter 5 - Functional Description**

This chapter provides descriptions of the functional operation of the major assembles contained in the 56100A Scalar Network Analyzer. The operation of each of the major circuit blocks is described. (The CRT monitor assembly is not covered in this chapter: this assembly is replaced as an entire unit.)

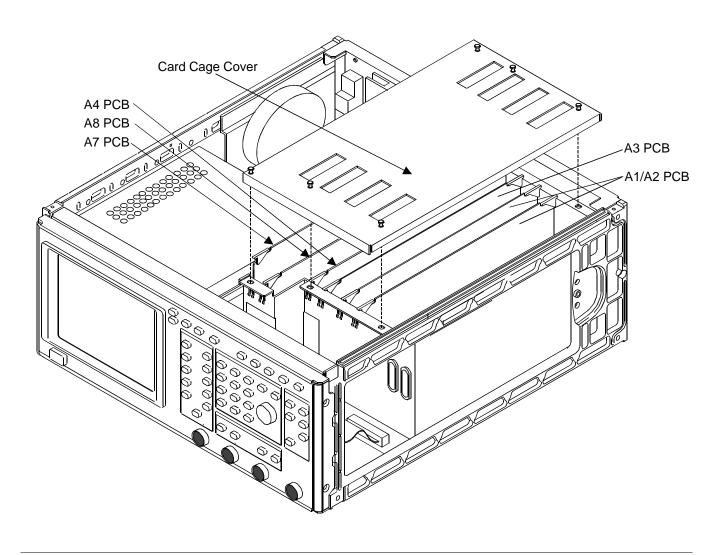

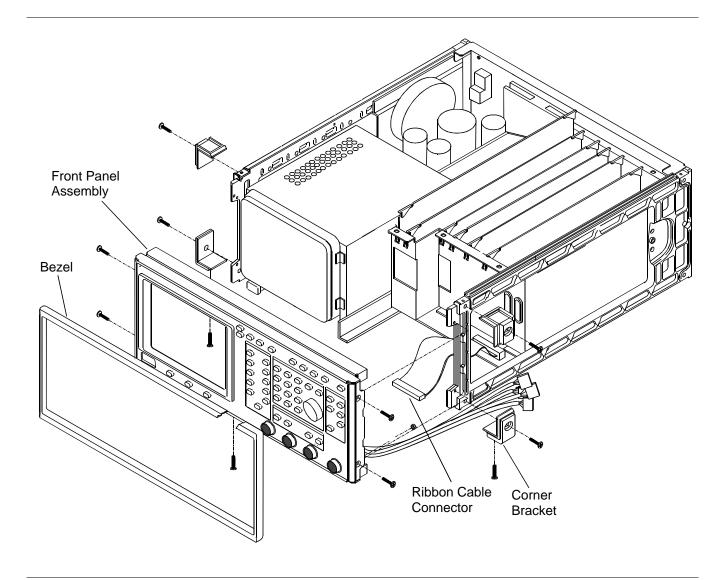

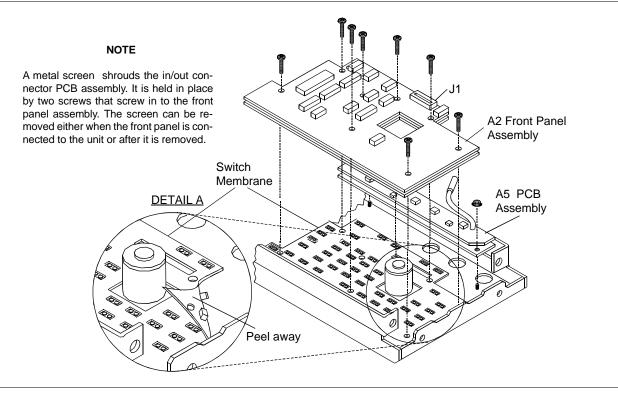

### Chapter 6 - Removal and Replacement Procedures

The disassembly procedures presented in this chapter describe how to gain access to the major 56100A assemblies and parts for troubleshooting or replacement.

#### Index

#### Appendix A - RF Detector Diode Replacement Procedures

This appendix contains the procedure for replacing defective detector diodes in model 5400-71B75 RF Detectors for replacing detector diode modules in series 560-7XXX RF Detectors. Series 5400-71XXX RF Detectors and series 560-7XXX RF Detectors are used with 540XXA systems.

56100A MM i/ii

### Chapter 1 General Information

# Table of Contents

| 1-1  | SCOPE OF THE MANUAL                                                                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2  | INTRODUCTION                                                                                                                                                                                                                             |

| 1-3  | IDENTIFICATION NUMBER                                                                                                                                                                                                                    |

| 1-4  | RELATED MANUALS                                                                                                                                                                                                                          |

| 1-5  | ONLINE MANUAL                                                                                                                                                                                                                            |

| 1-6  | NETWORK ANALYSIS DESCRIPTION 1-3                                                                                                                                                                                                         |

| 1-7  | $56100 \mathrm{A}\mathrm{SCALAR}$ NETWORK ANALYZER DESCRIPTION $$ $$ 1-4                                                                                                                                                                 |

|      | Measurement System Overview1-4Normalization and Measurement1-5Cursors, Markers, and Limit Lines1-6Averaging and Smoothing1-7Measurement Accuracy1-7Recommended Signal Sources1-8Stored Test Configuration Setups1-8GPIB Compatibility1-8 |

| 1-8  | OPTIONS                                                                                                                                                                                                                                  |

| 1-9  | ADDITIONAL EQUIPMENT REQUIRED 1-9                                                                                                                                                                                                        |

|      | SWR Autotester       1-9         Detectors       1-9                                                                                                                                                                                     |

| 1-10 | AVAILABLE ACCESSORIES                                                                                                                                                                                                                    |

|      | Extender Cables1-10GPIB Cables1-10Adapter Cables1-11Open/Short Calibration References1-11Other Accessories1-11                                                                                                                           |

| 1-11 | PERFORMANCE SPECIFICATIONS                                                                                                                                                                                                               |

| 1-12 | EXCHANGE ASSEMBLY PROGRAM                                                                                                                                                                                                                |

| 1-13 | STATIC SENSITIVE COMPONENT HANDLING PRECAUTIONS                                                                                                                                                                                          |

| 1-14 | RECOMMENDED TEST EQUIPMENT                                                                                                                                                                                                               |

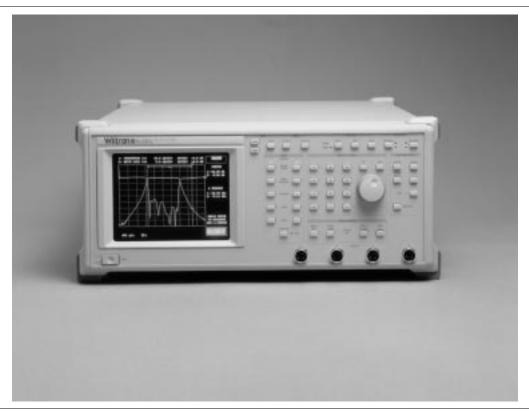

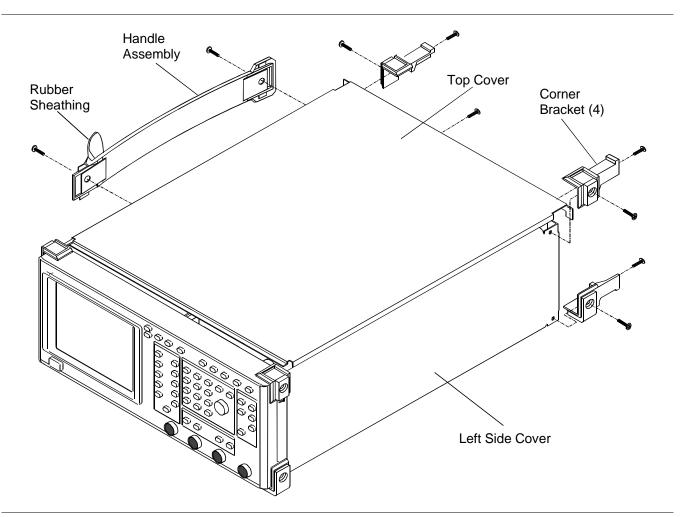

Figure 1-1. 56100A Scalar Network Analyzer

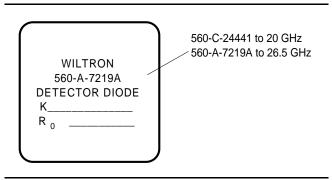

NOTE: ANRITSU Company was formerly known as WILTRON Company.

# Chapter 1 General Information

### 1-1 SCOPE OF THE MANUAL

This manual provides general information, performance verification, calibration, parts lists, and service information for the ANRITSU Model 56100A Scalar Network Analyzer. The Model 56100A is shown in Figure 1-1.

### 1-2 INTRODUCTION

This Section provides a general description of the equipment, the unit identification number, other related manuals, performance specifications, and instrument options, exchange assembly program, static handling procedures, and recommended test equipment.

# 1-3 IDENTIFICATION NUMBER

All ANRITSU instruments are assigned a unique six-digit ID number, such as K 701001. Each 56100A has an ID number affixed to the outside of the rear panel. Please use this number when ordering parts or corresponding with ANRITSU's Customer Service department.

### 1-4 RELATED MANUALS

This manual is one of a two manual set that consists of an Operating and Programming Manual (OPM) and a Maintenance Manual (MM). The ANRITSU part number for this manual is listed on the title page.

### 1-5 ONLINE MANUAL

This manual is available on CD ROM as an Adobe Acrobat™ (\*.pdf) file. The file can be viewed using Acrobat Reader™, a free program that is also available on the CD ROM. This file is "linked" such that the viewer can choose a topic to view from the displayed "bookmark" list and "jump" to the manual page on which the topic resides. The text can also be word-searched. Contact ANRITSU Customer Service for price and availability.

# 1-6 NETWORK ANALYSIS DESCRIPTION

Network analysis consists of the characterization of microwave devices through the measurement of the device transmission and impedance characteristics as a function of frequency. It includes the measurement of input match, output match, forward transmission, and reverse transmission. Each of these parameters is a complex quantity consisting of magnitude and phase.

56100A MM 1-3

A network analyzer system consists of three main elements: the signal source, the measurement components, and the network analyzer or signal processing element. There are two basic types of network analyzers: scalar and vector. Scalar network analyzers (SNAs) measure only the magnitude of the transmission or reflection signal. Vector network analyzers measure the magnitude and the phase of the transmission or reflection parameter. The 56100A is of the scalar network analyzer type.

# 1-7 56100A SCALAR NETWORK ANALYZER DESCRIPTION

The Model 56100A is a scalar network analyzer that has a frequency range of 10 MHz to 110 GHz, depending on the external test components and frequency sources used. (An external signal source is required for operation of this unit.) The Model 56100A is ideal for both production and R&D applications.

Measurement System Overview With the addition of a programmable signal source, the 56100A becomes an automated transmission, return loss (SWR), and power measurement system. For example, with the appropriate test components and an ANRITSU 68169B frequency source, the 56100A will operate over the 10 MHz to 40 GHz range from a single coaxial test port. The 56100A

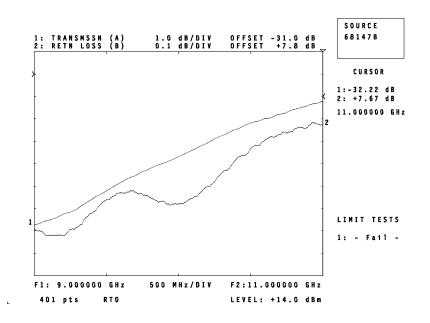

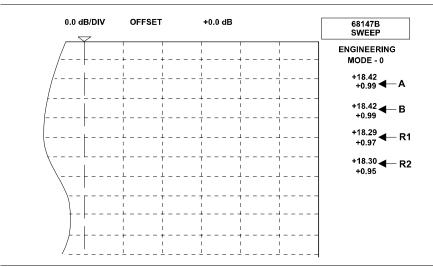

Figure 1-2. Typical 56100A Annotated Display

1-4 56100A MM

provides fully annotated displays of test data and measurement parameters as shown in Figure 1-2.

Under internal microprocessor control (no external controller required), the 56100A normalizes and simultaneously displays any two signals that are input on channels A, B, R1, and R2. The same inputs can be displayed as ratios A/R1, A/R2, B/R1, or B/R2. Depending on the external components used, the dynamic range for each channel is typically 76 dB (–60 dBm to +16 dBm). The noise floor is typically less than –62 dBm, providing a 76 dB (or greater) dynamic range for most applications.

Key 56100A features include:

- ☐ Automatic measurements and hard copy output without a controller.

- $\hfill\Box$  Accurate coaxial measurements from 10 MHz to 50 GHz.

- □ Nine stored setups to eliminate set-up time.

- ☐ Cursors, markers, and limit lines to improve productivity.

- □ Complete, annotated, step-by-step normalization and measurement procedures.

- □ Four measurement channels.

- □ Low cost.

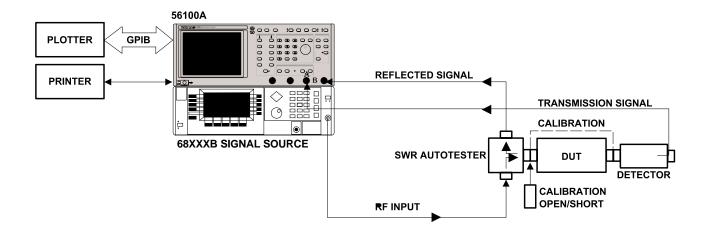

Figure 1-3. Typical 56100A Test Setup

56100A MM 1-5

Normalization and Measurement In a typical 56100A test setup, the test device is inserted between the SWR Autotester and the detector (refer to Figure 1-3). Detected signals from the SWR Autotester vary in proportion to the reflections, while the detector output varies in proportion to transmission loss or gain. The detector can be used to measure power in dBm.

During normalization, procedural guidance is automatically provided for transmission and return loss measurements. For a return loss test, a 0 dB reference is established by connecting an open, then a short, to the SWR Autotester test port. The normalization data are taken independent of sensitivity settings at the number of points selected, with 0.002dB resolution, and stored in memory for correction of test data or for recall. Furthermore, an algorithm interpolates between data points to hold interpolated test data accuracy usually to within ±0.1 dB. Once the 56100A has been normalized across a user-selected frequency range, measurements can be made over any portion of the range without renormalization. Set-up time is greatly reduced by storing parameters for up to nine test setups for later reuse.

During measurements, data is taken at 101, 201, or 401 points (user selected) with 0.002 dB vertical resolution on both channels. Typically, test data is updated every 100 ms, allowing "real time" adjustments of the test device. A permanent record of the test data – with or without the test, marker, or stored setup parameters – is made automatically using an HP 7440A, 7470A, or 7475A plotter. Most dotmatrix printers may also be used, including the the Cannon BJ30 Bubble Jet Printer. Since the 56100A requires only about 10 seconds for print formatting, a new test can be conducted while the previously taken data is being printed out.

The 56100A is equally effective when used for waveguide reflectometer setups, where ratio measurements may be preferred. The 560-10BX-1 Adapter Cables provide the interface between the instrument and waveguide detectors.

Cursors, Markers, and Limit Lines The 56100A has an extensive number of cursor functions available. These cursor functions are in addition to markers available when an ANRITSU 6600B, 6700A/B, or 68XXXB series signal generator is used as the system signal source. The 56100A communicates with the signal source through a dedi-

1-6 56100A MM

cated GPIB link and displays an identifier for each marker.

To speed the interpretation of data, complex limit lines can be entered by the user via the front panel keys or via the GPIB interface. Limit lines may have up to ten segments that may slope or step with frequency. Each segment of the limit line is numerically identified during entry.

Averaging and Smooth-ing

When characteristics of the test device vary rapidly with frequency at very low signal levels, the trace can be smoothed by use of the averaging and/or smoothing functions. The smoothing control has three selections: Off, Min, and Max. To maintain the accuracy of the measurement data, smoothing is performed by reducing bandwidth, rather than by averaging adjacent data points in order to preserve measurement detail.

When averaging is selected, 2 to 256 successive traces can be averaged to smooth the trace display. As various combinations of smoothing and averaging are selected, the trace update time is automatically adjusted.

### Measurement Accuracy

The return-loss accuracy of the 56100A is largely attributable to the high directivity of the ANRITSU SWR Autotesters. For example, the 560-97A50-1 Autotester with its GPC-7 test port connector has a directivity of better than 40 dB from 10 MHz to 18 GHz. The 560-98K50 has a directivity that exceeds 35 dB up to 18 GHz, 32 dB up to 26.5 GHz, and 30 dB up to 40 GHz. The same unit has a test port match of better than 23 dB up to 26.5 GHz and 15 dB up to 40 GHz. To avoid the use of error-producing adapters, SWR autotesters are available with either male or female test ports in Type N, WSMA, or K connectors. All have high directivity. When the GPC-7 test port is selected, the lowest reflection adapters obtainable are offered in Type N and WSMA, which is optimized for testing SMA devices.

The accuracy of a transmission loss, gain, or power measurement is affected by reflections from the test port, the device under test, and the detector. These errors are minimized by the very low reflections from the ANRITSU SWR autotesters and detectors.

56100A MM 1-7

Zero-biased Schottky diodes are used in all 560-7xxx series detectors to minimize drift and circuit complexity. With the exception of the 560-7K50, the diode modules of these units are field-replaceable. This eliminates the expense and inconvenience of returning the detectors to a service center for repair.

The accuracy of the 56100A is high also because modulation of the input signal is not required. The need for modulation is avoided by using self-balancing amplifiers, which are stable at low signal levels. As a result, errors from modulation asymmetry and modulation-sensitive test devices are nonexistent. Without the insertion loss of a modulator, measurements can be made at higher input levels. This increases the measurement dynamic range.

Recommended Signal Sources There are many advantages in selecting an AN-RITSU 6600B, 6700A/B, or 68XXXB series signal source for use with the 56100A. One advantage is the power sweep. In this mode, the output power is swept over a 15 dB range, which enhances gain compression measurements. In the alternate sweep mode, the 56100A can display frequency response over different frequency ranges and/or power levels.

Another advantage of using ANRITSU signal sources is that they use fundamental oscillators from 2 to 20 GHz, thus avoiding the serious errors introduced by the subharmonics of frequency multipliers.

Stored Test Configuration Setups Set-up time is reduced substantially by storing up to nine front-panel setups, four of which include the associated calibration data. A unique preview feature allows stored setup parameters to be reviewed before recalling or storing a new setup in the memory location. The stored data are backed by a battery with an estimated 5-year life.

GPIB Compatibility

The implementation of the IEEE-488 General Purpose Interface Bus (GPIB) is standard on the 56100A and provides remote control of all frontpanel functions except power on/off and CRT intensity. A high speed data transfer mode can be used to transfer measurement data to the host computer; this capability is especially useful in manufacturing environments where archiving of data is required.

1-8 56100A MM

### 1-8 options

The following standard instrument option is available:

Option 1, Rack Mount. This kit contains mounting brackets, chassis track slides, mounting ears and a chassis track slide with a full  $90^{\circ}$  tilt capability.

## 1-9 ADDITIONAL EQUIPMENT REQUIRED

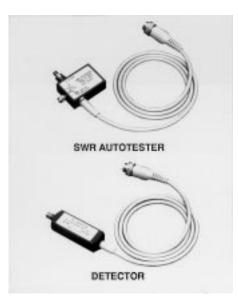

Either of the two pieces of equipment shown in Figure 1-4 below is required for normal 56100A operation.

### SWR Autotester

The 560 Series SWR Autotesters integrate in one small package a broadband, high directivity bridge, a detector, a low reflection test port, a reference termination, and a connecting cable. The output of the SWR Autotester is a detected signal, varying in proportion to reflections from the test device connected to the test port. Optional extender cables can be used without degradation in performance.

#### **Detectors**

The 560 Series detectors are used for coaxial transmission loss or gain and power measurements and also with coaxial adapters for waveguide reflectometer measurements. Zero-biased, field-replaceable Schottky diodes provide –60 dBm sensitivity. Optional extender cables can be used without degradation in performance.

Figure 1-4. 560 Series SWR Autotester and Detector

56100A MM 1-9

## 1-10 AVAILABLE ACCESSORIES

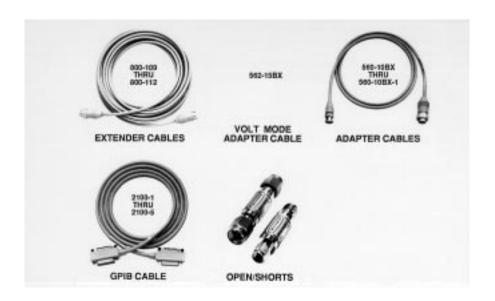

The accessories listed below and shown in Figure 1-5, are available for the 56100A.

Figure 1-5. Available Accessories for the 56100A

### Extender Cables

Extender cables can be installed between the SWR Autotester or detectors and the 56100A, permitting measurements up to 200 feet. The available lengths are:

- □ 7.6m (25 ft.), P/N 800-109

- □ 15.2m (50 ft.), P/N 800-110

- □ 30.5m (100 ft.), P/N 800-111

- □ 61m (200 ft.), P/N 800-112

#### **GPIB Cables**

The 2100- series cables interconnect instruments on the GPIB; the 2100-1 cable is provided with the 56100A. The available cable lengths are:

- □ 1m (3.3 ft.), P/N 2100-1

- □ 2m (6.6 ft.), P/N 2100-2

- □ 4m (13.2 ft.), P/N 2100-4

- □ 0.5m (1.65 ft.), P/N 2100-5

1-10 56100A MM

| bles                                    | female connectors allow the 56100A to be used with waveguide or other detectors with the same type of output connectors. Cable length is 122 cm (4 ft.):                                                                                  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | <ul><li>□ BNC Female, P/N 560-10BX</li><li>□ SMA Female, P/N 560-10BX-1</li></ul>                                                                                                                                                         |

|                                         | The 806- series of adapter cables are used to connect the 56100A to various sweep generators. The 806-7 cable is provided with the 56100A and is used to connect to ANRITSU 6600B and 6700A/B signal sources. Other cables available are: |

|                                         | <ul> <li>ANRITSU 56100A to HP 8350B, HP 8340A/B:</li> <li>P/N 806-13</li> </ul>                                                                                                                                                           |

|                                         | $\hfill\square$ ANRITSU 56100A to HP 8620C: P/N 806-14                                                                                                                                                                                    |

| Open/Short<br>Calibration<br>References | An Open/Short is used to establish a 0 dB return loss reference during the normalization procedure for the 56100A. The available calibration references are:                                                                              |

|                                         | ☐ GPC-7 Short Only                                                                                                                                                                                                                        |

|                                         | □ GPC-7                                                                                                                                                                                                                                   |

|                                         | □ K Male                                                                                                                                                                                                                                  |

|                                         | □ K Female                                                                                                                                                                                                                                |

|                                         | □ N Male                                                                                                                                                                                                                                  |

|                                         | □ N Female                                                                                                                                                                                                                                |

|                                         | □ WSMA Male                                                                                                                                                                                                                               |

|                                         | □ WSMA Female                                                                                                                                                                                                                             |

| Other Accesso-                          | Other accessories for the 56100A include:                                                                                                                                                                                                 |

|                                         | □ A transit case for the RF components                                                                                                                                                                                                    |

|                                         | □ A transit case for the instrument itself                                                                                                                                                                                                |

|                                         | ☐ A 260 mm (10.25 in.) diagonal external monitor                                                                                                                                                                                          |

$\hfill\Box$ A Cannon BJ30 Ink Jet Printer

56100A MM 1-11

### 1-11 PERFORMANCE SPECIFICATIONS

Performance specifications for the 56100A are listed in the Technical Data Sheet located in Appendix A of the 56100A Operating Manual. They are also included as part of the procedures contained in Chapter 2 of this manual.

## 1-12 EXCHANGE ASSEMBLY PROGRAM

ANRITSU maintains a module exchange program for selected subassemblies. If a malfunction occurs in one of these subassemblies, the defective item can be exchanged. Upon receiving your request, ANRITSU will ship the exchange subassembly to you, typically within 24 hours. You then have 45 days in which to return the defective item. All exchange subassemblies are warranted for 90 days from the date of shipment, or for the balance of the original equipment warranty, whichever is longer.

Please have the exact model number and serial number of your unit available when requesting this service, as the information about your unit is filed according to the instrument's model and serial number. For more information about the program, contact your local ANRITSU Sales Company or ANRITSU Customer Service:

ANRITSU Company ATTN: Customer Service 490 Jarvis Drive Morgan Hill, CA 95037-2809

Telephone: (408)-778-2000 FAX: (408)-778-0239

ANRITSU Tables 1-1 and 1-2 provide a listing of replaceable subassemblies for the 56100A.

# 1-13 STATIC SENSITIVE COMPONENT HANDLING PRECAUTIONS

The 56100A contains components that can be damaged by static electricity. Figure 1-6 (page 1-15) illustrates the precautions that should be followed when handling static-sensitive subassemblies and components. If followed, these precautions will minimize the possibilities of static-shock damage to these items.

#### NOTE

Use of a grounded wrist strap when removing and/or re-placing subassemblies or parts is strongly recommended.

## 1-14 RECOMMENDED TEST EQUIPMENT

Table 1-3 page (1-16) provides a list of recommended test equipment needed to check and service the 56100A Scalar Network Analyzer.

1-12 56100A MM

Table 1-1. Replaceable Subassemblies Listing

| Replaceable Subassembly               | ANRITSU Part Number |

|---------------------------------------|---------------------|

| A1/A2 Signal Channel PCB Assy         | D42005-3            |

| A2 Front Panel Interface PCB Assy     | D40036-7            |

| A3 Signal Channel Interface PCB Assy  | D42003-3            |

| A4 Sweeper Interface PCB Assy         | D32659-3            |

| A5 Input Connector PCB Assy           | C42002-3            |

| A7 CPU PCB Assy                       | D42001-3            |

| A8 Graphics System Processor PCB Assy | D42004-3            |

| A9 Motherboard PCB Assy               | D42000-3            |

| A12 Power Supply Assy                 | D32521-3            |

| Monitor Assy                          | D40047              |

| Front Panel Assy                      | B42055              |

| Rear Panel Assy                       | B42056              |

| Cable Assy, Main Power Switch         | C42033              |

| Power Supply Line Transformer         | D32572              |

Table 1-2. Replaceable Parts Listing (1 of 2)

| Description                                          | Part Number |

|------------------------------------------------------|-------------|

| Cover, Top                                           | D40107      |

| Cover, Bottom                                        | D40107      |

| Cover, Side ( Handle)                                | 2000-633    |

| Cover, Side                                          | D42021      |

| Handle, Side Carrying                                | 783-830     |

| Screw, Handle, Side Carrying                         | 900-714     |

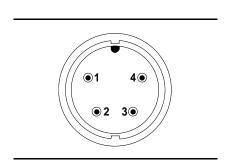

| Connector, Front Panel Input                         | 551-152     |

| Foot, Rear, Bottom Left                              | 2000-548    |

| Foot, Rear, Bottom Right                             | 2000-549    |

| Foot, Rear, Top Left                                 | 2000-552    |

| Foot, Rear, Top Right                                | 2000-553    |

| Screw, Green Head                                    | 2000-560    |

| Fuse, 2A, Antisurge, 3AG (110/120 Vac Operation)     | 631-62      |

| Fuse, 1A, Antisurge, 5x20 mm (220/240 Vac Operation) | 631-63      |

| Fuse Holder, 3AG                                     | 553-221     |

| Fuse Holder, 5 x 20 mm                               | 553-240     |

| Fan Assembly, Rear Panel                             | C40217      |

| Finger Guard, Fan (with filter, aluminum)            | 790-442     |

| Knob, Data Entry                                     | 2000-641    |

| Line Module Assembly, Rear Panel                     | 260-13      |

56100A MM 1-13

Table 1-2. Replaceable Parts Listing (2 of 2)

| 2000-546<br>2000-547<br>2000-550 |  |

|----------------------------------|--|

| 2000-547                         |  |

|                                  |  |

| 2000-550                         |  |

| 2000 000                         |  |

| 2000-551                         |  |

|                                  |  |

| B37147                           |  |

| C37170                           |  |

| C37171                           |  |

| D37168-3                         |  |

| D37169-3                         |  |

|                                  |  |

1-14 56100A MM

Do not touch exposed contacts on any static sensitive component.

2. Do not slide static sensitive component across any surface.

Do not handle static sensitive components in areas where the floor or work surface covering is capable of generating a static charge.

4. Wear a static-discharge wristband when working with static sensitive components.

5. Label all static sensitive devices.

6. Keep component leads shorted together whenever possible.

7. Handle PCBs only by their edges. Do 8. not handle by the edge connectors.

Lift & handle solid state devices by their bodies – never by their leads.

Transport and store PCBs and other static sensitive devices in staticshielded containers.

#### 10. ADDITIONAL PRECAUTIONS:

- Keep workspaces clean and free of any objects capable of holding or storing a static charge.

- Connect soldering tools to an earth ground.

- Use only special anti-static suction or wick-type desoldering tools.

Figure 1-6. Static Sensitive Component Handling Procedures

56100A MM 1-15

Table 1-3. Recommended Test Equipment

| INSTRUMENT                                                                                                                                                     | CRITICAL<br>SPECIFICATION                                          | RECOMMENDED<br>MANUFACTURER/MODEL       | USE*    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|---------|

| Adaptor Cable                                                                                                                                                  | Simulates 560-7 Series detectors                                   | ANRITSU Model 560-10BX                  | C, P    |

| Adapters<br>(50Ω impedance)                                                                                                                                    | Type N (male) to BNC (male)<br>Type N (female) to BNC (male)       | HP1250-0176<br>HP1250-0082              | C, P    |

| Connector Cable                                                                                                                                                | Connects sweep generator signal for 56100A compatibility           | ANRITSU 806-7                           | C, P, O |

| GPIB Cable                                                                                                                                                     | Connects 56100A to 68147B via dedicated bus                        | ANRITSU 2100-1                          | C, P, O |

| RF Detector                                                                                                                                                    | 0.01 to 20 GHz                                                     | ANRITSU Model 560-7N50B                 | C, P, O |

| Digital Multimeter  Resolution: 4-1/2 digits (to 20V)  DC Accuracy: 0.002% + 2 counts  DC Input Impedance: 10 MΩ  AC Accuracy: 0.07% + 100 counts  (to 20 kHz) |                                                                    | John Fluke Mfg Co. Inc.,<br>Model 8840A | С       |

|                                                                                                                                                                |                                                                    | Tektronix, Inc.<br>Model 2445           | C, P    |

| Power Meter, with: Power Range: +10 to -55 dBm Other: 50 MHz Calibrated Output  Anritsu Corp., N                                                               |                                                                    | Anritsu Corp., Model ML4803A            | C, P    |

| Power Sensor $50\Omega$ input                                                                                                                                  | Frequency Range: 1.0 MHz to 2.0 GHz<br>Power Range: -30 to +20 dBm | Anritsu Corp., Model MA4601A            |         |

| Frequency Source Frequency Range: 0.01 to 20 GHz Power Range: +10 dB to -60 dBm  ANRITSU Model 681XXB Series ANRITSU Model 683XXB Series                       |                                                                    | C, P, O                                 |         |

| Step Attenuator  Attenuation Range: 60 dB, 10 dB/step 0.000 to 18.0 GHz                                                                                        |                                                                    | Hewlett-Packard, Model 8495B            | C, P    |

| Voltage Standard Range: -1.462V to -1.313 mV Accuracy: 0.002% of set value.                                                                                    |                                                                    | John Fluke Mfg Co. Inc.,<br>Model 335D  | C, P    |

$<sup>^{\</sup>star}$  C = Calibration, P = Performance verification, O = Operational

1-16 56100A MM

# Chapter 2 Performance Verification

## **Table of Contents**

| 2-1 | INTRODUCTION                                                                                                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-2 | RECOMMENDED TEST EQUIPMENT 2-3                                                                                                                                       |

| 2-3 | VERIFYING SIGNAL CHANNEL ACCURACY 2-3                                                                                                                                |

| 2-4 | DC VOLTAGE METHOD                                                                                                                                                    |

| 2-5 | RF TEST METHOD                                                                                                                                                       |

| 2-6 | INHERENT UNCERTAINTIES IN RF TEST METHOD 2-11                                                                                                                        |

|     | Detector/Source Match Interaction Uncertainty2-11Sweep Generator Harmonics2-11Step Attenuator Accuracy2-11Detector Frequency Response2-11Signal Channel Accuracy2-11 |

| 2-7 | PERFORMANCE TEST RECORD 2-11                                                                                                                                         |

|     | DC Voltage Method Verification Test                                                                                                                                  |

# Chapter 2 Performance Verification

2-1 INTRODUCTION

This section provides two procedures for verifying signal channel accuracy, the only test necessary to ensure that the 56100A provides proper performance. These two procedures provide alternative methods for checking signal channel accuracy.

2-2 RECOMMENDED TEST EQUIPMENT

Table 1-1 (Chapter 1) provides a listing of recommended test equipment for both the DC and RF methods. If the recommended items are not available, equipment with equivalent characteristics may be substituted.

2-3 VERIFYING SIGNAL CHANNEL ACCURACY

Two methods for verifying signal channel accuracy are described in this section. The first and most accurate is the DC Voltage Method, which uses highly accurate dc voltages applied directly to the signal channel being verified. Using this method, measurement uncertainties are negligible (provided that the recommended test equipment is used.) The second method is the RF Method that has measurement uncertainties attributable to the source, attenuator, and detector.

56100A MM 2-3

### 2-4 DC VOLTAGE METHOD

The dc voltage method uses highly accurate dc voltages to simulate input RF power without introducing source errors. A 560-10BX adapter cable must be used to connect the dc voltage to the input of the 56100A.

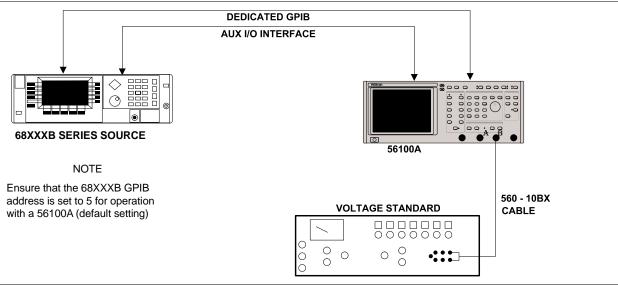

- **Step 1.** Set up the test equipment as shown in Figure 2-1.

- Step 2. Connect the 560-10BX cable to input A on the 56100A.

- *Step 3.* Press the Power keys on the 56100A and 68147B to On.

- **Step 4.** On the 56100A:

- Press the System Menu key.

- Using the Menu up/down keys, highlight RESET (TO FACTORY SETTINGS) and press the Select key (this resets both the 56100A and 68147B).

- Press the Channel 2 Display On/Off Key to Off.

- Ensure that INTERFACE OFF is not displayed on the bottom line and that frequencies are annotated correctly.

- Press the Channel 1 Menu key.

- Using the Menu up/down keys, highlight **POWER**.

- Press the Select key.

Figure 2-1. Test Equipment Setup, DC Voltage Method

2-4 56100A MM

- Press the Cursor Measurements On/Off key to On.

- **Step 5.** On the 68147B:

- Go to the Configure RF Menu and press the Retrace RF key to On.

- Step 6. Set the DC voltage source to zero volts. Press the Calibration key and select LOW LVL TRIM from the displayed menu.

| Num-<br>ber | DC Voltage | CURSOR<br>dBm Reading |

|-------------|------------|-----------------------|

| 1           | -1.462V    | +16, +0.25; -0.10     |

| 2           | -0.6208V   | +9, +0.12; -0.10      |

| 3           | -1.313 mV  | -26, ±0.34            |

- **Step 7.** Adjust the voltage standard to provide voltage 1 in table at left.

- Step 8. On the 56100A, verify that the CURSOR dBm value displayed in the menu area is within the tolerances listed in the table at left.

- Step 9. Increment the voltage standard output to voltages 2 and 3, in turn, and repeat steps 7 and 8 (above). For voltage 3, press the Smoothing key to light both LEDs (maximum smoothing).

- Step 10. Move the 560-10BX cable to input B.

- **Step 11.** On the 56100A:

- Press the Channel 1 Menu key.

- Using the Menu up/down keys, highlight SELECT IN-PUT from the displayed menu.

- Press the Select key.

- Using the Menu up/down keys, highlight B.

- Press the Select key.

- Press the Cursor Measurements On/Off key to restart the numerical display in the menu area.

- Repeat steps 6 thru 9 for input B.

- Repeat steps 9 and 10 for R1 and R2. In the procedure, substitute "R1" and "R2," respectively, for "B".

56100A MM 2-5

### 2-5 RF TEST METHOD

The RF method for verifying signal channel accuracy has inherent measurement inaccuracies. These inaccuracies are explained in paragraph 2-6. Tables 2-1 and 2-2 list the expected accuracy limits and error sources introduced by the test equipment during these measurements. Table 2-1 has space where the Cursor dBm Readings may be recorded for these measurements.

Power Meter/Power Sensor Calibration at 50 MHz

- Step 1. Position the CAL FACTOR control on the power meter to the necessary calibration power factor as specified on the power sensor chart.

- Step 2. Zero set the power meter.

- Step 3. Connect the power sensor to the POWER REF connector. With the POWER REF ON, adjust the CAL ADJ potentiometer for 0.00 dBm on the power meter display.

- Step 4. Disconnect the power sensor from the POWER REF connector.

Sweep Generator/Step Attenuator Output Power Calibration

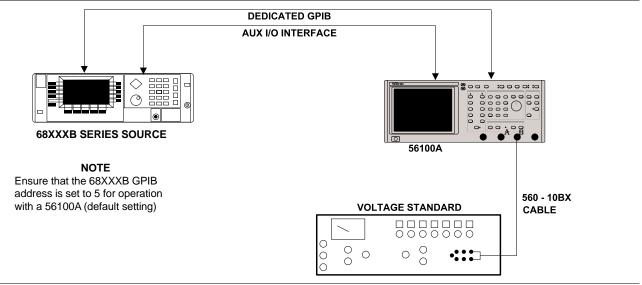

- **Step 1.** Set up the test equipment as shown in Figure 2-2.

- Step 2. Press the Power keys on the 56100A and 68147B to On.

- **Step 3.** On the 56100A:

- Press the System Menu key.

Figure 2-2. Test Equipment Setup, RF Method

2-6 56100A MM

Table 2-1. Power Accuracy with Recommended Test Equipment

| Attenuator Dial Setting | Input Power Level (dBm) | Cursor dBm Reading | RSS Limits (dBm) |

|-------------------------|-------------------------|--------------------|------------------|

| 0                       | 10                      |                    | 10.6 to 9.5      |

| 10                      | 0                       |                    | 0.6 to -0.5      |

| 20                      | -10                     |                    | −9.4 to −10.5    |

| 30                      | -20                     |                    | −19.4 to −20.5   |

| 40                      | -30                     |                    | -29.3 to -30.6   |

| 50                      | -40                     |                    | −39.3 to −40.7   |

| 60                      | -50                     |                    | -49.0 to -50.9   |

Table 2-2. Effect of Possible Error Sources on Measurement (RF Method)

| Input         | Possible Error (dB) at 50 MHz   |                              |                     |                                |                            |              |

|---------------|---------------------------------|------------------------------|---------------------|--------------------------------|----------------------------|--------------|

| Powr<br>(dBm) | Det/Source Match<br>Interaction | Harmonic Frequency at 30 dBc | Attenuator Accuracy | Detector Frequency<br>Response | Signal Channel<br>Accuracy | RSS Error    |

| +16           | ±0.31                           | +0.6<br>-0.4                 | ±0.3                | +0.3<br>-0.2                   | +0.25<br>-0.1              | +0.8<br>-0.7 |

| +10           | ±0.28                           | +0.3<br>-0.2                 | ±0.3                | +0.3<br>-0.2                   | +0.15<br>-0.1              | +0.6<br>-0.5 |

| 0             | ±0.14                           | +0.3<br>-0.2                 | ±0.3                | +0.3<br>-0.2                   | ±0.2                       | +0.6<br>-0.5 |

| -10           | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±0.25                      | +0.6<br>-0.5 |

| -20           | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±0.3                       | +0.6<br>-0.5 |

| -30           | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±0.4                       | +0.7<br>-0.6 |

| -40           | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±0.5                       | ±0.7         |

| -50           | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±0.8                       | +1.0<br>-0.9 |

| <b>-</b> 55   | ±0.14                           | +0.15<br>-0.1                | ±0.3                | +0.3<br>-0.2                   | ±1.0                       | ±1.1         |

- Using the Menu up/down keys, highlight RESET (TO FACTORY SETTINGS).

- Press the Select key (this resets both the 56100A and 68147B).

- **Step 4.** On the 68147B, go to the Configure RF Menu and press the Retrace RF key to On.

- **Step 5.** On the 355D:

- Position the attenuator dial to 10.

- Connect the power sensor to the output.

56100A MM 2-7

### **Step 6.** On the 68147B:

- Press the CW/Sweep Select key to go to the CW Menu display.

- Press the Edit F1 key, and set F1 for 50 MHz.

- Press Edit F1 and set the output power for +5 dBm (nominal) using the keypad.

- Using the rotary data knob, adjust the output power to indicate −5 dBm on the power meter display.

- Record the indicated output power level from the 68147B Level display.

- Set the level to +10 dBm (nominal) using the keypad.

- Using the rotary data knob, adjust the output power to indicate 0.00 dBm on the power meter display.

- Record the indicated output power level from the Level display.

### Channel A Power Accuracy Test

### **Step 1.** On the 355D:

- Remove the power sensor.

- Connect the detector.

- $\blacksquare$  Set the dial to 0.

- Step 2. On the 68147B, go to the Configure RF Menu and press the Retrace RF key to Off.

### **Step 3.** On the 56100A:

- Press the Channel 2 Display On/Off key to Off

- Press the Channel 1 Menu key.

- Using the Menu up/down keys, highlight **POWER**.

- Press the Select key.

- Press the Cursor Measurements On/Off key to On.

2-8 56100A MM

- Step 4. Press the System Menu key and select data points. Set the data points to 101.

- **Step 5.** Tabulate results as follows: Record the CURSOR readout from the display into Table 2-2, on the line for the corresponding Attenuator Dial Setting.

- **Step 6.** On the 355D and 56100A, tabulate as in step 4, above, for settings of 10, 20, 30, and 40.

#### **NOTE**

Smoothing should be off throughout these tests.

- Step 7. Position the 355D to 50.

- **Step 8.** On the 56100A:

- Press the Averaging key.

- Use the Menu up/down keys to highlight 32 averages and Select.

- **Step 9.** Tabulate the results as described in step 4, above.

- Step 10. Position the 355D to 60.

- **Step 11.** On the 56100A:

- Press the Averaging key. Use the up/down keys to highlight 128 sweeps and press select.

- Step 12. Tabulate as described in step 1, above. The readout corresponds to a -50 dBm input power level.

- **Step 13.** On the 68147B:

- Press the Edit F1 key, and using the keypad enter the level as recorded during "Sweep Generator/Step Attenuator Output Power Calibration" in step 6 (5th bullet) on page 2-8.

- Averaging starts automatically when the 68147B changes level.

- Tabulate as described in step 4, above. The readout corresponds to -55 dBm input power level.

56100A MM 2-9

Channel B Power Accuracy Test

### **Step 1.** On the 56100A:

- Press the Averaging key twice to turn averaging off.

- Press the Channel 1 Menu key.

- Using the Menu up/down keys, highlight SELECT IN-PUT.

- Press the Select key.

- Using the Menu up/down keys, highlight B.

- Press the Select key.

- Move the detector to the B input.

- Press the Cursor Measurements On/Off key to On to restore the numerical display in the menu area.

### **Step 2.** On the 68147B:

- Press the Edit F1 key.

- Using the keypad and appropriate terminator key, set the output power for the value recorded in Step 6 (last bullet) on page 2-8.

- **Step 3.** On the 355D, position the attenuator dial to 0.

- **Step 4.** Go to page 2-8 and repeat Steps 2 thru 13 as listed for the Channel A Power Accuracy Test.

Channels R1 and R2 Power Accuracy Tests

Repeat the procedure or the Channel A Power Accuracy Test for inputs R1 and R2. Substitute "R1" and "R2," respectively, for "A."

2-10 56100A MM

# 2-6 INHERENT UNCERTAINTIES IN RF

The power measurement method using the recommended test equipment listed in Table 1-1 (Chapter 1) and shown in Figure 2-2 contains inherent measurement uncertainties. These uncertainties are explained in the following paragraphs.

Detector/Source

Match Interaction Uncertainty

The impedance mismatch between the RF source and the RF detector contributes a possible uncertainty known as source match. For the 68147B and the 560-7 Series detectors, this uncertainty is as follows:

At +10 dBm (355D Attenuator Dial at 0), the source match of the sweep generator and the mismatch of the RF detector interact to produce an overall uncertainty of  $\pm 0.28$  dB.

At 0 dBm and below (355D Attenuator Dial between 10 and 60), the source match of the 355D and the RF detector interact to produce an uncertainty of  $\pm 0.14$  dB.

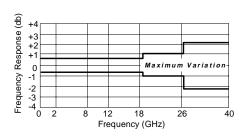

Figure 2-3. Detector Frequency Response

Sweep Generator Harmonics

In the linear range of the RF detector (between +16 dBm and approximately -15 dBm) harmonics of the sweep generator fundamental frequency contribute to errors in the measurement.

Step Attenuator Accuracy

The HP355D step attenuator has a specified accuracy of ±0.3 dB from dc to approximately 50 MHz. This possible error in accuracy is present at all attenuator dial settings, including zero.

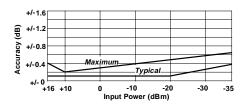

Figure 2-4. Channel Accuracy

Detector Frequency Response

Signal Channel Accuracy The frequency response of the Model 560-7 detector introduces a further possible error as shown in Figure 2-3.

The accuracy varies with input power as shown in Figure 2-4. Be advised that the values used in Table 2-4 are factory test values. They are much tighter than the published accuracy as shown in Figures 2-3 and 2-4.

# 2-7 PERFORMANCE TEST RECORD

Copies of sample performance test records are provided below in Tables 2-3 and 2-4. These test records provide the means for maintaining an accurate and complete record of instrument performance. We recommend that you copy these pages and record on them the results from your initial testing of the 56100A. These initial readings can later be used as benchmark values for future tests of the same serial-numbered instrument.

56100A MM 2-11

DC Voltage Method Verification Test Table 2-3 below provides a place for recording the values measured for Inputs A, B, R1 and R2 during the DC Voltage Method channel verification test.

Table 2-3. Sample Test Record for DC Voltage Method Verification Test

### Input A, Channel 1

| Number | DC Voltage | CURSOR dBm Reading (Spec) | CURSOR dBm Reading Rec'd |

|--------|------------|---------------------------|--------------------------|

| 1      | -1.462V    | +16, +0.25; -0.10         |                          |

| 2      | -0.6208V   | +9, +0.12; -0.10          |                          |

| 3      | −1.313 mV  | -26, ±0.34                |                          |

### Input B, Channel 1

| Number | DC Voltage | CURSOR dBm Reading (Spec) | CURSOR dBm Reading Rec'd |

|--------|------------|---------------------------|--------------------------|

| 1      | -1.462V    | +16, +0.25; -0.10         |                          |

| 2      | -0.6208V   | +9, +0.12; -0.10          |                          |

| 3      | –1.313 mV  | -26, ±0.34                |                          |

### Input R1, Channel 1

| Number | DC Voltage | CURSOR dBm Reading (Spec) | CURSOR dBm Reading Rec'd |

|--------|------------|---------------------------|--------------------------|

| 1      | -1.462V    | +16, +0.25; -0.10         |                          |

| 2      | -0.6208V   | +9, +0.12; -0.10          |                          |

| 3      | −1.313 mV  | -26, ±0.34                |                          |

### Input R2, Channel 1

| Number | DC Voltage | CURSOR dBm Reading (Spec) | CURSOR dBm Reading Rec'd |

|--------|------------|---------------------------|--------------------------|

| 1      | -1.462V    | +16, +0.25; -0.10         |                          |

| 2      | -0.6208V   | +9, +0.12; -0.10          |                          |

| 3      | –1.313 mV  | -26, ±0.34                |                          |

RF Method Verification Test Table 2-4 below provides a place for recording the values measured for Inputs A, B, R1 and R2 during the RF Method channel verification test. We recommend that you copy these pages and record on them the results from your initial testing of the 56100A.

2-12 56100A MM

Table 2-4. Sample Test Record for RF Method Verification Test

### Input A, Channel 1

| Attenuator Dial Setting | Input Power Level (dBm) | Cursor dBm Reading | Limits (dBm)   |

|-------------------------|-------------------------|--------------------|----------------|

| 0                       | 10                      |                    | 10.6 to 9.5    |

| 10                      | 0                       |                    | 0.6 to -0.5    |

| 20                      | -10                     |                    | −9.4 to −10.5  |

| 30                      | -20                     |                    | −19.4 to −20.5 |

| 40                      | -30                     |                    | −29.3 to −30.6 |

| 50                      | -40                     |                    | −39.3 to −40.7 |

| 60                      | -50                     |                    | -49.0 to -50.9 |

| 60                      | -55                     |                    | -53.9 to -56.1 |

Input B, Channel 1

| Attenuator Dial Setting | Input Power Level (dBm) | Cursor dBm Reading | Limits (dBm)   |

|-------------------------|-------------------------|--------------------|----------------|

| 0                       | 10                      |                    | 10.6 to 9.5    |

| 10                      | 0                       |                    | 0.6 to -0.5    |

| 20                      | -10                     |                    | −9.4 to −10.5  |

| 30                      | -20                     |                    | −19.4 to −20.5 |

| 40                      | -30                     |                    | -29.3 to -30.6 |

| 50                      | -40                     |                    | -39.3 to -40.7 |

| 60                      | -50                     |                    | -49.0 to -50.9 |

| 60                      | <b>–</b> 55             |                    | -53.9 to -56.1 |

### Input R1, Channel 1

| Attenuator Dial Setting | Input Power Level (dBm) | Cursor dBm Reading | Limits (dBm)   |

|-------------------------|-------------------------|--------------------|----------------|

| 0                       | 10                      |                    | 10.6 to 9.5    |

| 10                      | 0                       |                    | 0.6 to -0.5    |

| 20                      | -10                     |                    | −9.4 to −10.5  |

| 30                      | -20                     |                    | −19.4 to −20.5 |

| 40                      | -30                     |                    | -29.3 to -30.6 |

| 50                      | -40                     |                    | -39.3 to -40.7 |

| 60                      | -50                     |                    | -49.0 to -50.9 |

| 60                      | <b>-</b> 55             |                    | -53.9 to -56.1 |

56100A MM 2-13

Table 2-4. Sample Test Record for RF Method Verification Test (Cont.)

### Input R2, Channel 1

| Attenuator Dial Setting | Input Power Level (dBm) | Cursor dBm Reading | Limits (dBm)   |

|-------------------------|-------------------------|--------------------|----------------|

| 0                       | 10                      |                    | 10.6 to 9.5    |

| 10                      | 0                       |                    | 0.6 to -0.5    |

| 20                      | -10                     |                    | −9.4 to −10.5  |

| 30                      | -20                     |                    | −19.4 to −20.5 |

| 40                      | -30                     |                    | -29.3 to -30.6 |

| 50                      | -40                     |                    | -39.3 to -40.7 |

| 60                      | -50                     |                    | −49.0 to −50.9 |

| 60                      | <b>–</b> 55             |                    | -53.9 to -56.1 |

2-14 56100A MM

# Chapter 3 Adjustments

# Table of Contents

| 3-1 | INTRODUCTION                         | 3-3 |

|-----|--------------------------------------|-----|

| 3-2 | RECOMMENDED TEST EQUIPMENT           | 3-3 |

| 3-3 | ADJUSTMENT PROCEDURES                | 3-3 |

| 3-4 | SWEEP RAMP AMPLIFIER GAIN ADJUSTMENT | 3-7 |

| 3-5 | CRT MONITOR ADJUSTMENTS              | 3-8 |

# Chapter 3 Adjustments

### 3-1 INTRODUCTION

This chapter contains the adjustment procedures for the Model 56100A. A performance verification test, using the DC Voltage Method, is also included at the end of paragraph 3-3. These procedures are usually used when out-of-specification conditions are noted during the Performance Verification tests of Chapter 2, or as a result of subassembly/component repair or replacement.

- 3-2 RECOMMENDED TEST EQUIPMENT

- Table 1-1 (Chapter 1) lists the recommended test equipment for performing the adjustment procedures contained in this section.

- 3-3 ADJUSTMENT PROCEDURES

To perform the adjustment procedures, the top cover and the PCB card clamp must be removed.

- **Step 1.** Set up the test equipment as shown in Figure 3-1.

- Step 2. With the 56100A off, press the Power key on the 68147B and allow the self test to finish.

- Step 3. Press the Reset key on the 68147B.

Figure 3-1. Test Equipment Setup, DC Voltage Method

56100A MM 3-3

**Step 4.** Press the 56100A Power key and allow the self test to finish.

#### **NOTE**

Unless otherwise specified, the 56100A is the instrument referred to in the following steps.

- **Step 5.** Press the System Menu key.

- Step 6. Use the Menu up/down keys to highlight RESET.

- Step 7. Press the Select key.

- **Step 8.** Press the Channel 2 Display On/Off key to turn off the corresponding LED.

- Step 9. Press the Channel 1 Menu key.

- Step 10. Use the Menu up/down keys to highlight POWER.

- *Step 11.* Press the Calibration key.

- **Step 12.** Repeatedly press Down cursor key until Log/Temp correction is highlighted.

- Step 13. Press the Select key.

#### **CAUTION**

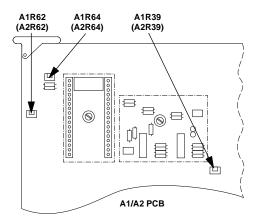

Be careful not to disturb the front panel keys when making the following A1/A2 PCB adjustments.

- Step 14. Connect the 560-10BX cable to the A input. Leave the BNC end of the cable disconnected.

- Step 15. Adjust A2R62 for  $0.00 \pm 0.01$ , as read on the LOG/TEMP CORRECTION display (see Figure 3-2).

- **Step 16.** Remove the cable from the A input and connect it to the B input.

- **Step 17.** Adjust A2R64 for  $0.00 \pm 0.01$ .

- *Step 18.* Remove the cable and connect it to the R1 input.

- **Step 19.** Adjust A1R62 for  $0.00 \pm 0.01$ .

- Step 20. Remove the cable and connect it to the R2 input.

3-4 56100A MM

Figure 3-2. Monitor Display of LOG/TEMP CORRECTION

Figure 3-3. A1/A2 PCB Adjustments

- **Step 21.** Adjust A1R64 for  $0.00 \pm 0.01$ .

- Step 22. Press the Cursor Measurements On/Off key to On. A cursor display should appear on the upper right side of the monitor screen.

- Step 23. Set the voltage standard for a -0.6208V output, which is equivalent to +9 dBm.

- Step 24. Connect the cable to the A input.

- Step 25. Connect the BNC end of the cable to the voltage standard.

- Step 26. Adjust A2R39 until the cursor readout is +9 dBm ±0.02 dB.

56100A MM 3-5

- Step 27. Press the Channel 1 Menu key.

- Step 28. Toggle the Menu up/down keys to highlight SELECT IN-PUT.

- Step 29. Press the Select key.

- Step 30. Use the Menu up/down keys to highlight R1.

- Step 31. Press the Select key.

- **Step 32.** Leaving the BNC end of the cable connected to the voltage standard, connect the other end to the R1 input.

- *Step 33.* Press the Cursor Measurements On/Off key to Off to restore the cursor display.

- Step 34. Adjust A1R39 until the cursor readout is +9 dBm ±0.02 dB.

### **NOTE**

Steps 35 through 55 constitute a performance verification test utilizing the DC Voltage Method.

- **Step 35.** Disconnect the BNC end of the cable from the voltage standard, and connect the other end to the A input.

- Step 36. Press the Channel 1 Menu key.

- Step 37. Toggle the Menu up/down keys to highlight SELECT IN-PUT.

- Step 38. Press the Select key.

- Step 39. Use the Menu up/down keys to highlight A.

- Step 40. Press the Select key.

- *Step 41.* Press the Calibration key.

- Step 42. Using the Menu up/down keys, highlight LOW LVL TRIM.

- **Step 43.** Press the Select key twice. Wait until the NULLING message disappears and a cursor display appears.

- **Step 44.** Adjust the voltage standard to provide Voltage 1 in the table at left.

- Step 45. Connect the BNC end of the cable to the voltage standard.

3-6 56100A MM

| Number | DC Voltage | CURSOR dB<br>Reading |

|--------|------------|----------------------|

| 1      | -1.462V    | +16, 0.25; 0.10      |

| 2      | -0.6208V   | 9, 0.12; -0.10       |

$-26, \pm 0.34$

-1.313 mV

**Step 46.** Verify that the displayed CURSOR dBm value is within the tolerances listed in the above table.

Step 47. Increment the voltage standard output to voltages 2 and 3, in turn, and verify that the displayed CURSOR dBm value is within the tolerances listed in the table. When using voltage 3, set smoothing to minimum by pressing the Smoothing key to light the top LED.

- Step 48. Disconnect the BNC end of the cable from the voltage standard, and connect the other end to input B.

- Step 49. Press the Channel 1 Menu key.

- Step 50. Using the Menu up/down keys, highlight SELECT INPUT.

- Step 51. Press the Select key.

- Step 52. Using the Menu up/down keys, highlight B.

- Step 53. Press the Select key.

- Step 54. Repeat steps 41 through 47 above.

- **Step 55.** Repeat steps 48 through 54 for R1 and R2. In the procedure, substitute R1 and R2, respectively, for B.

## 3-4 SWEEP RAMP AMPLIFIER GAIN ADJUSTMENT

This procedure covers adjustment of the Sweeper Interface (A4) PCB Assembly, using a 56100A chassis and a 56100A PCB Extender card. This procedure is only required after repair or replacement of the A4 PCB.

Connect a function generator to an oscilloscope. On the function generator, select a triangular waveform and a frequency of 100 Hz. Set the amplitude to 13V peak to peak while monitoring the signal on the oscilloscope. Adjust the offset so that the upper limit of the signal is +12V and the lower limit is -1V.

Ensure that the 56100A is not in Ramp Output mode by using the Reset feature. Without altering any of its settings, disconnect the function generator from the oscilloscope and connect it to the BNC connector marked Horizontal Input/Output on the rear panel.

Attach a x10 probe to the oscilloscope. Connect the probe to TP2 and the ground clip to TP6 (0V).

The oscilloscope should show a triangular wave of 100 Hz at  $\approx\!10~V_{p\text{-}p}$  amplitude. Adjust R10 until the upper limit of the waveform is exactly 10V above the 0V level. This completes the adjustment and verification of the Sweep Ramp circuit.

56100 MM 3-7

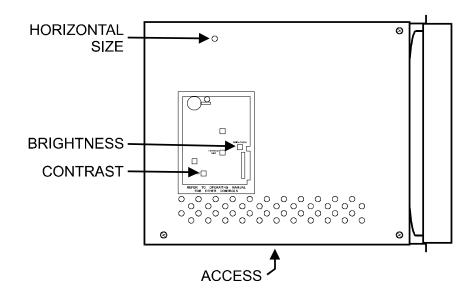

## 3-5 CRT MONITOR ADJUSTMENTS

These procedures are used to adjust the CRT monitor brightness, contrast, and horizontal size. Perform this procedure whenever a new CRT monitor assembly or Graphics Processor PCB has been installed. All other CRT monitor adjustments should be performed by qualified service personnel only.

### **WARNING**

Hazardous voltages are present inside the instrument when ac line power is connected. These procedures should only be performed by service personnel who are fully aware of the potential hazards associated with high voltage.

### Required Equipment

☐ Adjustment of the CRT horizontal size requires the use of a plastic or nylon hex alignment tool. Do not use metal tools to adjust CRT monitor settings.

### Preliminary

☐ Remove the 56100A top and left side covers, then set them back loosely in place.

### NOTE

For this procedure, it is important that a consistent temperature be maintained within the unit. These adjustments must be made with the instrument at normal operating temperature.

#### Brightness and Contrast Adjustment

- Step 1. Refer to the locator drawing on the CRT Monitor assembly top cover and locate the brightness and contrast trim pots, accessible through the side opening (Figure 3-4).

- Step 2. Reset the instrument.

- **Step 3.** Using the front panel INTENSITY control, set the display to intensity level 9.

- **Step 4.** Carefully adjust the brightness and contrast trim pots until the display just starts to "bloom" or distort.

- **Step 5.** Set the display intensity to level 1.

- **Step 6.** Adjust, if required, the brightness and contrast to achieve a level that is just visible.

3-8 56100A MM

- **Step 7.** Repeat steps 2 through 6 until the desired intensity levels at 1 and 9 are achieved.

- Step 8. Replace the 56100A top and left side covers.

- **Step 9.** Verify that the adjustment remains as desired throughout the operating temperature range of the instrument.

Figure 3-4. CRT Monitor Adjustments

### Horizontal Size Adjustment

- Step 10. Remove the 56100A top cover.

- Step 11. Insert a plastic or nylon hex alignment tool through the access hole (see Figure 3-4) and carefully adjust the horizontal size coil until the display is centered on the CRT.

- Step 12. Replace the 56100A top and side covers.

- **Step 13.** Verify that the adjustment remains as desired throughout the operating temperature range of the instrument.

56100 MM 3-9/3-10

# Chapter 4 Troubleshooting

## Table of Contents

| 4-1 | INTRODUCTION                         | 4-3 |

|-----|--------------------------------------|-----|

| 4-2 | TROUBLESHOOTING PROCEDURES           | 4-3 |

|     | 56100A Control Panel LED Error Codes |     |

## Chapter 4 Troubleshooting

4-1 INTRODUCTION

This chapter provides troubleshooting information for the 56100A Scalar Network Analyzer.

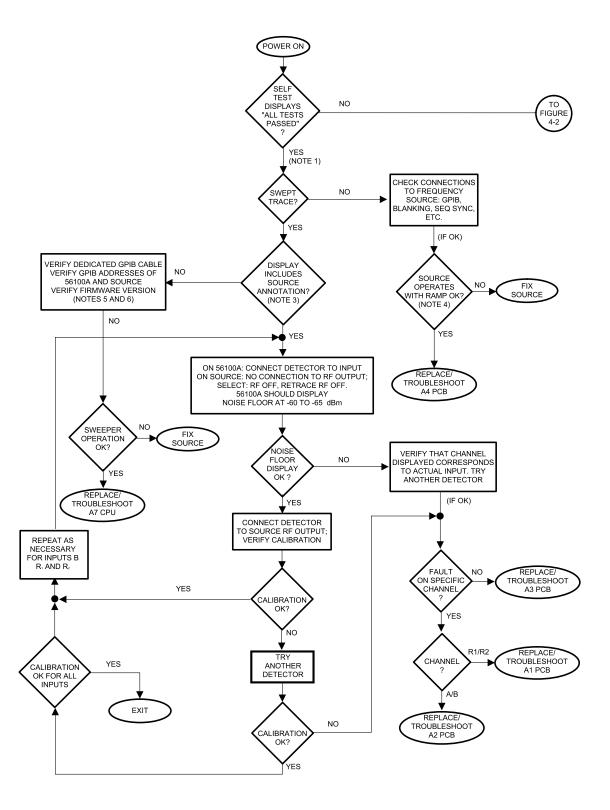

4-2 TROUBLESHOOTING PROCEDURES

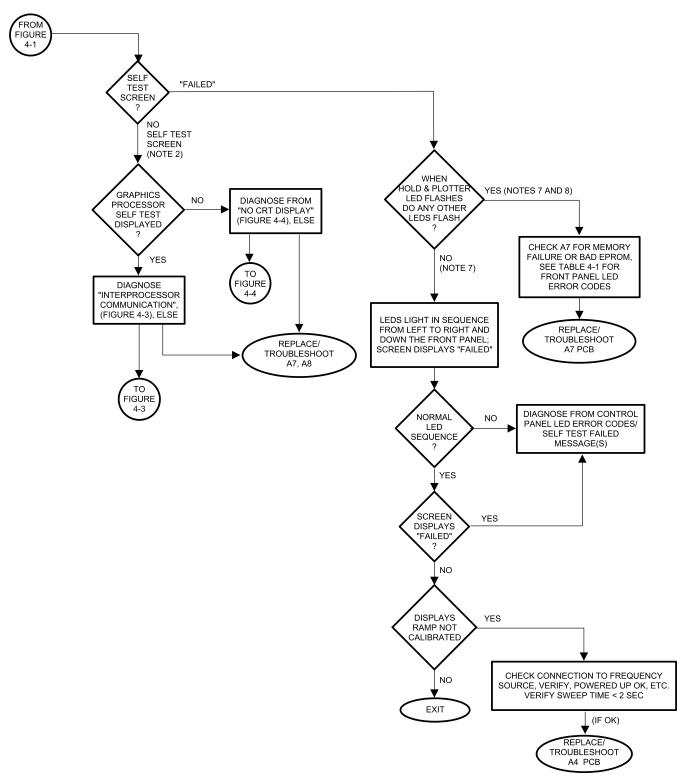

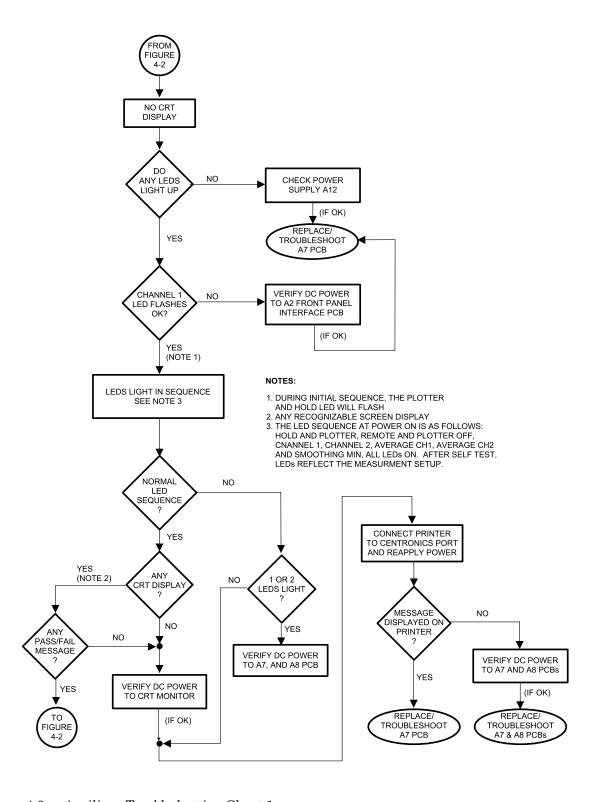

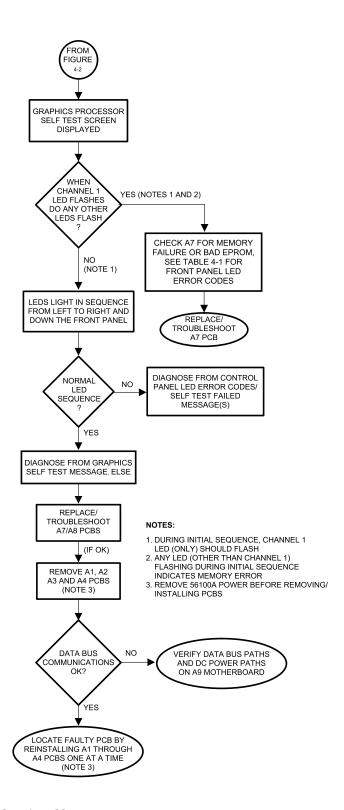

Tables 4-1 and 4-2 list the Control Panel LED Error Codes for the 56100A. Figures 4-1 and 4-2 are the main troubleshooting chart. Table 4-2 contains notes for the troubleshooting chart. Figures 4-3 and 4-4 are auxiliary troubleshooting charts.

Table 4-1. Control Panel LED Error Codes

| FLASHING LED*    | FAULT                                  | FAULT LOCATION                            |

|------------------|----------------------------------------|-------------------------------------------|

| Top Averaging    | Ramp Not Calibrated                    | A4, or Sweep Ramp Too Slow                |

| Top Smoothing    | CPU EPROM Checksum                     | A7 CPU (Observe Initial Test To Identify) |

| Bottom Averaging | CPU RAM Failure                        | A7 CPU                                    |

| Bottom smoothing | Front Panel Keyboard Interface Failure | Front Panel                               |

| Hold             | 7210 GPIB Interface Failure            | A7 CPU                                    |

| Plotter          | ADC Converter                          | A3 PCB                                    |

| Remote           | Channel R1/R2 PCB Not Detected         | A1 (A3) PCB                               |

| Printer          | Channel A/B PCB Not Detected           | A2 (A3) PCB                               |

| Uncal            | Channel R1/R2 PCB Null/Zero Failure    | A1 (A3) PCB                               |

| Display CH1      | Channel A/B PCB Null Zero Failure      | A2 (A3) PCB                               |

|                  |                                        | •                                         |

<sup>\*</sup> After a period of flashing, the option is given, at the user's discretion, to continue to attempt operation by pressing SELECT.

Table 4-2. Memory Test LED Error Codes

| Flashing Led*    | Fault              | Fault Location |

|------------------|--------------------|----------------|

| Hold and Plotter | Memory Test Result | N/A            |

| Top Averaging    | U36 RAM Failure    | A7 CPU PCB     |

| Bottom Averaging | U30 EPROM Checksum | A7 CPU PCB     |

| Top Smoothing    | U31 EPROM Checksum | A7 CPU PCB     |

| Bottom Smoothing | U32 EPROM Checksum | A7 CPU PCB     |

56100A MM 4-3

56100A Control Panel LED Error Codes When the 56100A is turned on, or when Self Test is selected, the analyzer undergoes a comprehensive self test. If this test passes, the message "ALL TESTS PASSED" is displayed; however, if any part of the self test fails, a descriptive error message is displayed. Additionally, a control panel LED flashes, indicating a fault condition exists. A different control panel LED flashes for each different type of fault condition. The control panel LED associated with each type of fault is listed in Table 4-1.

56100A Troubleshooting Charts

To use the troubleshooting charts for the Model 56100A: start at the top of the main troubleshooting chart (Figures 4-1 and 4-2) and proceed down the chart, performing the operations indicated. Refer to the auxiliary troubleshooting charts contained in Figure 4-3 and Figure 4-4 whenever so directed by the main troubleshooting chart. The notes for the main troubleshooting chart (Figures 4-1 and 4-2) are listed below in Table 4-2.

The suspected fault location will be indicated as a PCB or circuit location. If a replacement PCB is available, swap out the suspected PCB indicated by the chart. Otherwise, troubleshoot as applicable.

#### Table 4-3. Notes for Troubleshooting Charts

- 1. 56100A should start swept trace display, if connected to frequency source.

- 2. 56100A Text and Graphics processor should display short message indicating possible faults.

- 3. "Intellegent" sweepers only (ANRITSU 6600 series, or equivalent); all others ignore this step.

- 4. Sweep time of frequency source should be less than 2 seconds, maximum.

- 5. Verify cable connections and GPIB addresses for 56100A and for frequency source.

- 6. Frequency source firmware revision requirements:

6600A (with Memory Expansion)

6600B

8.07/6.05 or subsequent

6700A

6.13/3.0 or subsequent

6700B

7.04/4.01 or subsequent

HP 8350B

Refer to instrument manual.

HP 8341

Refer to instrument manual.

- 7. During initial portion of self test sequence, Hold and Plotter LEDs (only) should flash.

- 8. Any LED flashing simultaneously with the Hold and Plotter LEDs during self test indicates memory error.

- 9. If memory failure is not total, then self test failure message will identify probable failed IC.

4-4 56100A MM

Figure 4-1. Main Troubleshooting Chart

56100A MM 4-5

Figure 4-2. Main Troubleshooting Chart

4-6 56100A MM

Figure 4-3. Auxiliary Troubleshooting Chart 1

56100A MM 4-7

Figure 4-4. Auxiliary Troubleshooting Chart 2

4-8 56100A MM

# Chapter 5 Functional Description

## **Table of Contents**

| Ę | 5-1 | INTRODUCTION                                                                                                                                                                                                                                         |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

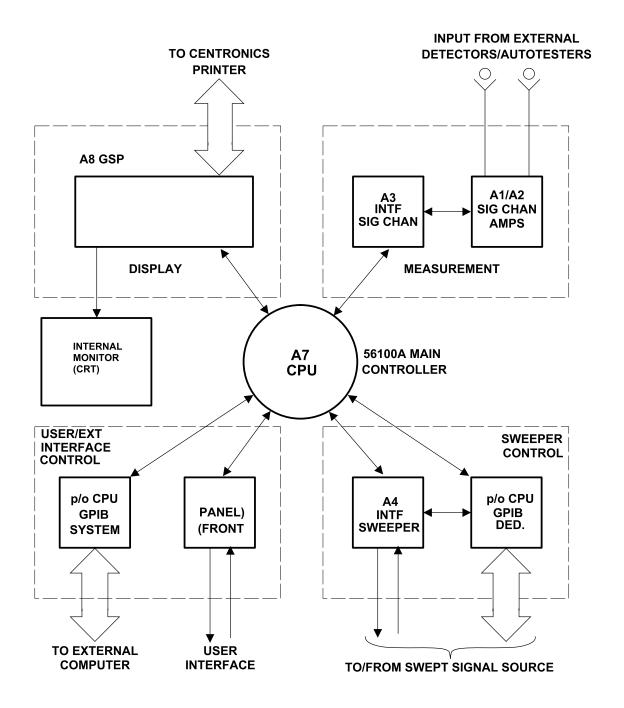

| Ę | 5-2 | OVERVIEW OF 56100A OPERATION 5-5                                                                                                                                                                                                                     |

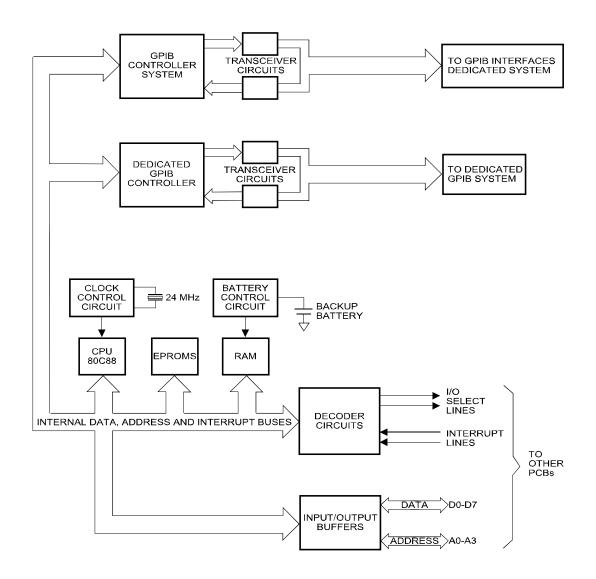

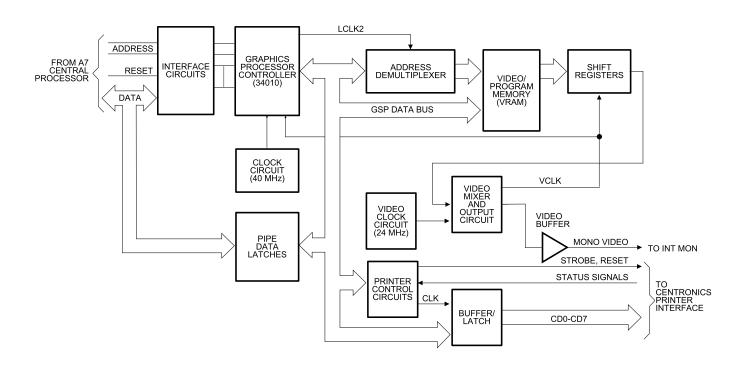

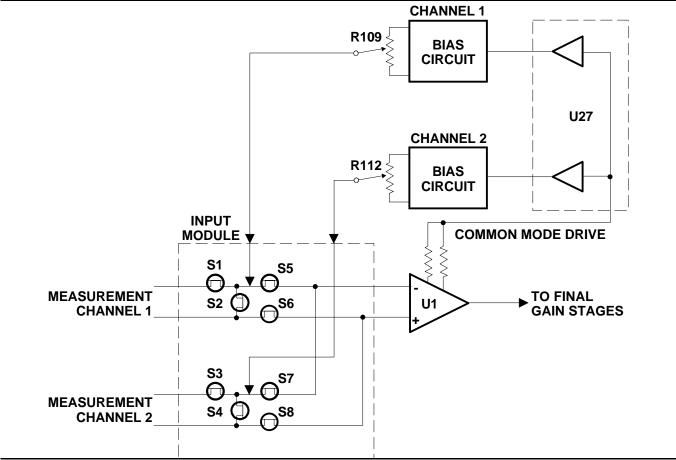

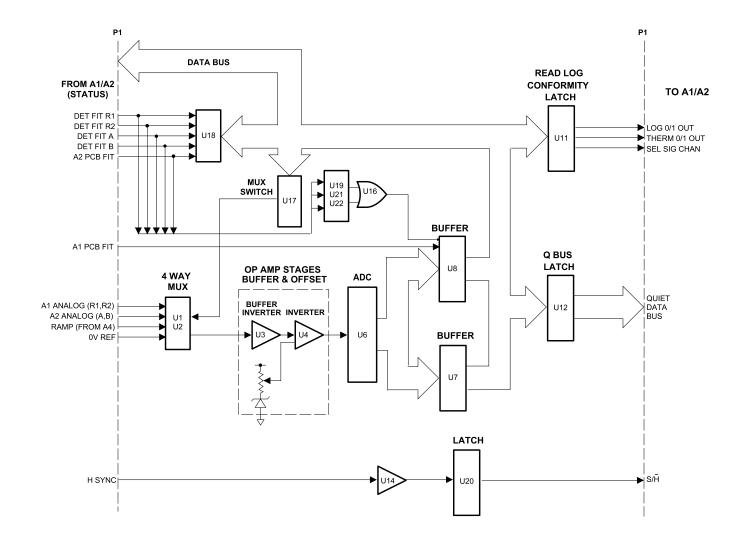

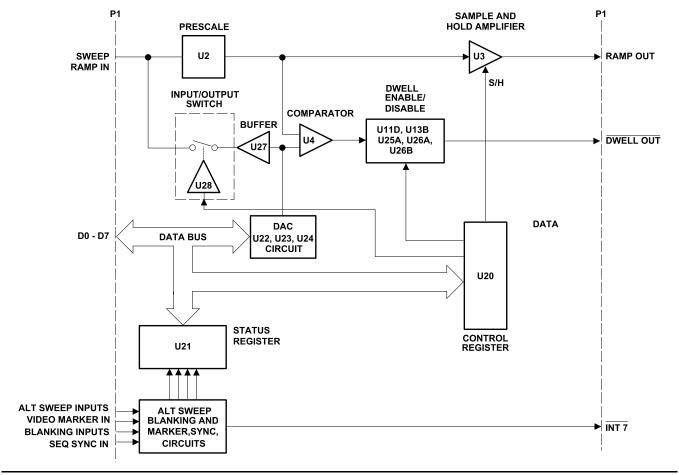

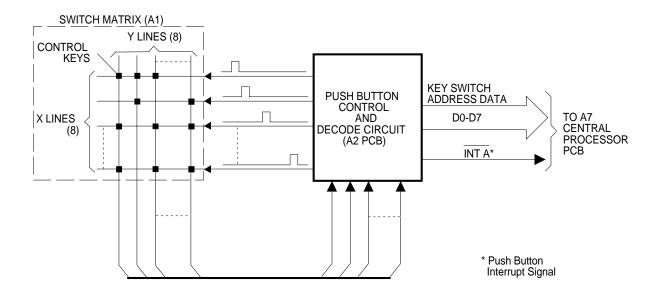

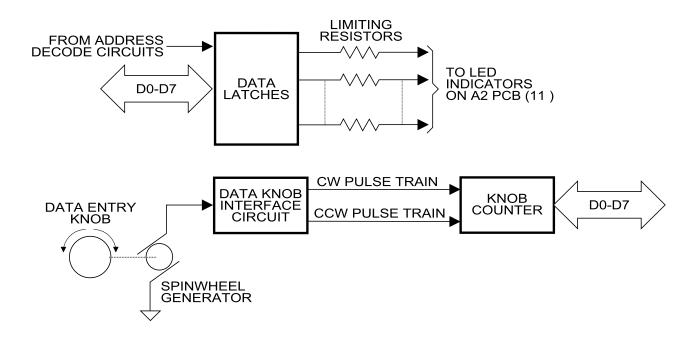

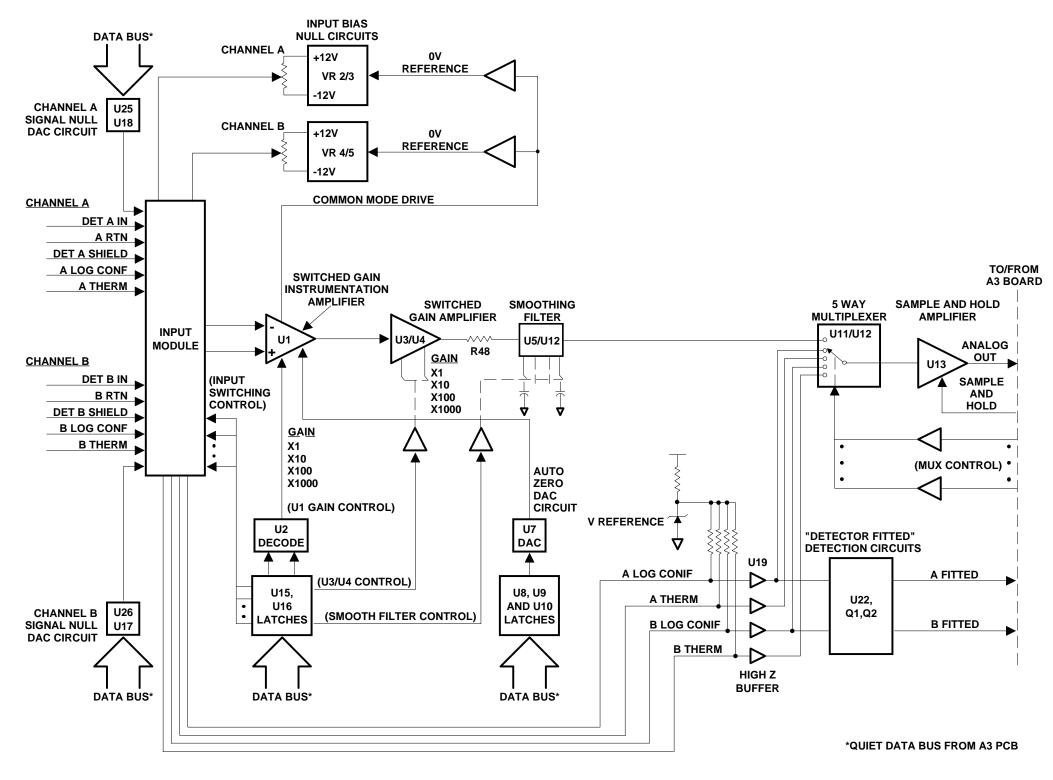

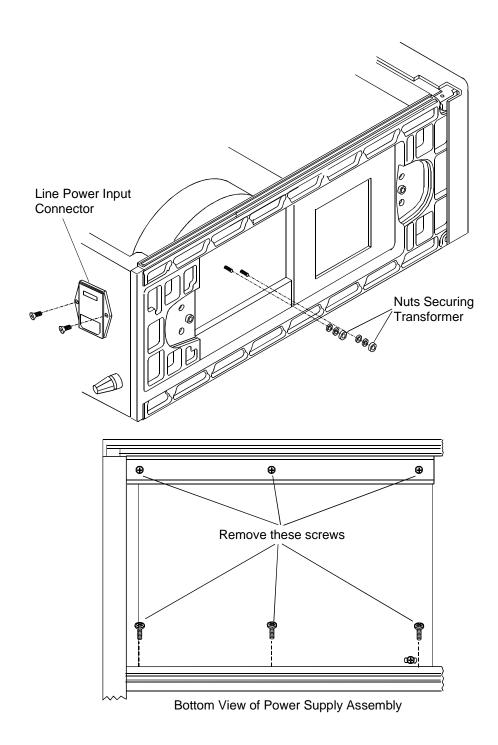

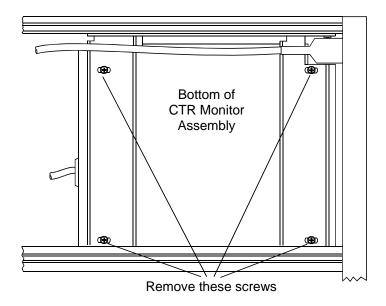

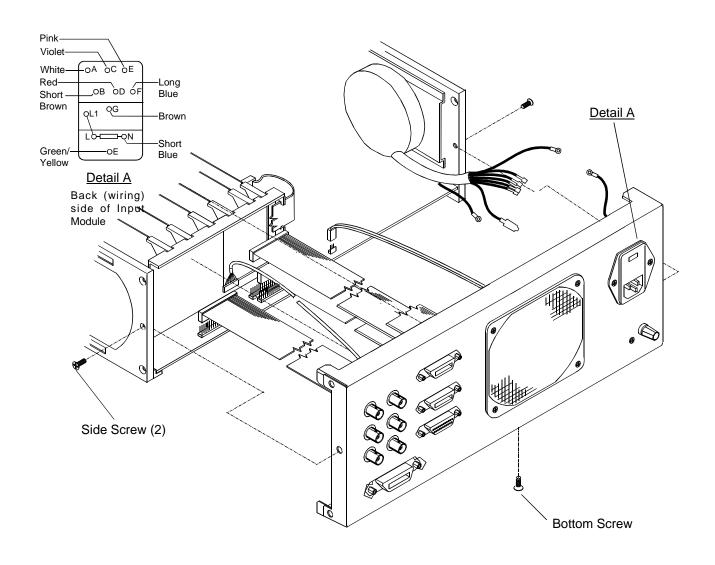

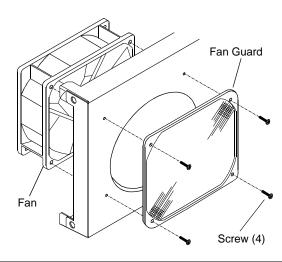

|   |     | The Measurement Process5-5Sweeper Interface and Control5-7Main CPU5-7Screen Display and Hardcopy Output5-8GPIB Functions5-8Miscellaneous 56100A Functions5-8                                                                                         |