## **TECHNICAL NOTE**

# **Newest Information and Further ITU-T O.172 Study Items**

ANRITSU CORPORATION

Copyright © 2004 by ANRITSU CORPORATION

The contents of this manual shall not be disclosed in any way or reproduced in any media without the express written permission of Anritsu Corporation

|                           |                                                           | MBP-1SG040142       |

|---------------------------|-----------------------------------------------------------|---------------------|

|                           |                                                           |                     |

|                           |                                                           | Provide a r         |

|                           | t Information and I<br>J-T 0.172 Study Ite                |                     |

|                           |                                                           |                     |

|                           | August 2004                                               |                     |

|                           | IP Network Division                                       |                     |

|                           | Anritsu Corporation                                       |                     |

| Discover What's Possible™ | Newest information and further study items of ITU-T 0.172 | IP Network Division |

Good Morning (Afternoon). Today I am going to introduce some new topics related to standardization of the jitter testing presently being examined by the ITU-T SG4/Q5 group.

| 4 Summary                           | G4/Q5 Meeting Resu                                                                          |               |

|-------------------------------------|---------------------------------------------------------------------------------------------|---------------|

| Outcome of last<br>(a) Revised drat | meeting (2004.05.03–04)<br>ft O.172 (TD30-PLEN)<br>son to NIST (TD31-PLEN)<br>s (TD35-PLEN) |               |

| Both Appendix V agenda for the r    | VII and Appendix VIII on Draft O.17<br>next meeting.                                        | 72 are on the |

|                                     |                                                                                             |               |

|                                     |                                                                                             |               |

| Discover What's Possible™           | Newest information and further study                                                        |               |

The previous meeting of the SG4/Q5 group was held on May 3 and 4 this year in Geneva, Switzerland. These three topics were the outcome of that meeting.

Currently, with respect to Appendix VII and VIII related to examination of jitter testers under O.172, we have identified securing measurement precision and clarifying measurement uncertainties. These subjects have been classified as Under Study for discussion and examination by the next meeting. The latest version of Draft O.172 reflecting these contents has been assigned the revised document number TD30-PLEN. With respect to item (b), a liaison statement letter has been drafted to request checking of the Appendix VII and VIII jitter tester verification methods by NIST as a third-party testing organization.

Item (c) covers the review of the Living List for future tasks.

| ITU-T SG4/Q5 Meeting Results (2/2)                                                                                                                                                                                                                                                                      |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Next meeting<br>To reach an agreement at the next SG4 meeting, an interim meeting will<br>be held in the UK from 2004.09.27–30.                                                                                                                                                                         |   |

| Liaison<br>The Anritsu proposal (D184) was agreed and SG4/Q5 decided to send a<br>liaison to NIST as a third party to give advice about measurement<br>accuracy in verification methods (Appendix VII, VIII). The same<br>information will be sent unofficially to NPL in the UK and PTT in<br>Germany. |   |

| Discover What's Possible™ Newest information and further study items of ITU-T 0.172 IP Network Division                                                                                                                                                                                                 | 3 |

The next general meeting of ITU-T SG4 is planned to be held in Geneva, Switzerland in March 2005. Prior to that, an interim meeting of experts will be held in the UK to clarify the current results which will then be presented to the next general meeting in 2005 for the purpose of obtaining official consent.

Anritsu proposed a jitter tester verification method under O.172 Appendix VII and VIII for checking by an impartial third party and, in addition to sending the results to NIST, unofficial checks by NPL in the UK and PTT in Germany have also been requested.

| Further Study Items for 0.172 Ap                                                    | pendix VII, VIII          |

|-------------------------------------------------------------------------------------|---------------------------|

| The following points for guaranteeing accuracy were                                 | e raised at the last      |

| ITU-T SG4/Q5 meeting to be resolved soon.                                           |                           |

| Appendix VII                                                                        |                           |

| 1. No certain way to verify final output jitter value                               |                           |

| → No known way to confirm standardized value at Acc                                 | uracy Map, so unable to   |

| separate errors of receiver from those of transmitter                               |                           |

| <ul> <li>Jitter errors at data generator not considered at all circuit)</li> </ul>  | (assuming ideal no-jitter |

| 2. Can't measure exact pattern jitter value that is factor                          | in measurement errors     |

| 3. Need to review circuit block diagram that can remove                             | e pattern jitter (One     |

| company informed last meeting that they hold patent                                 | for current method)       |

| Appendix VIII                                                                       |                           |

| 1. Need to verify edge-insertion method accuracy                                    |                           |

|                                                                                     |                           |

| Discover What's Possible™ Newest information and further study items of ITU-T 0.172 | IP Network Division       |

At the previous meeting in May this year, the contents of the Appendix VII and VIII jitter tester verification methods were introduced.

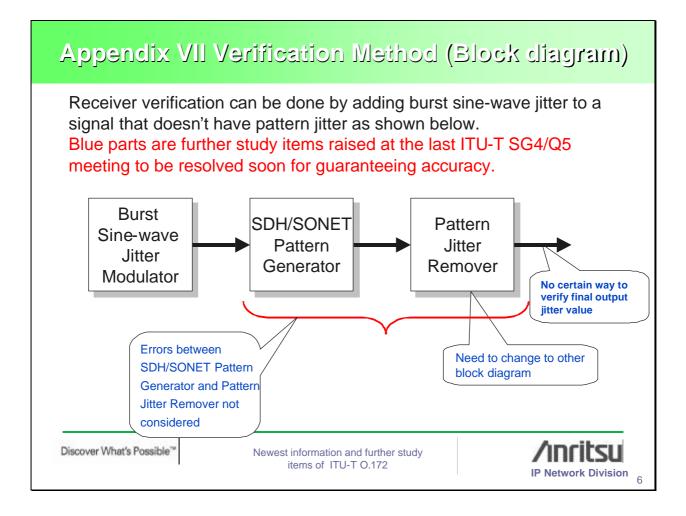

In the Appendix VII method, evaluation is performed by imposing a burst sinusoidal signal with 100 mUIpp jitter onto a data signal from which pattern jitter has been removed and these three issues were identified.

There is no certain way to verify the amount of jitter in the final output signal that is jitter modulated by the burst sine-wave modulation signal.

There is no way of accurately verifying the amount of jitter (less than 10 mUlpp) in the data signal from which pattern jitter has been removed.

Currently, since Company A has a patent on block diagram for the jitter-removal circuit described as a reference example in Appendix VII, it is clear that users will be prohibited from using the verification method, and as a result, it is necessary revise the block diagram so that all users will be able to use the method without patent licensing issues. The Appendix VIII method has the same configuration as jitter generation measurement in which a sampling oscilloscope is used to separate the amount of jitter in the reference signal into DJ and RJ for evaluation. In this method, the jitter at the part of the NRZ signal with no edge is evaluated, requiring validation of the edge-insertion method in terms of the previously standardized Hold method (copying jitter of previous edge).

From here on, I am going to explain the issues of the current Appendix VII method using block diagrams and figures, etc.

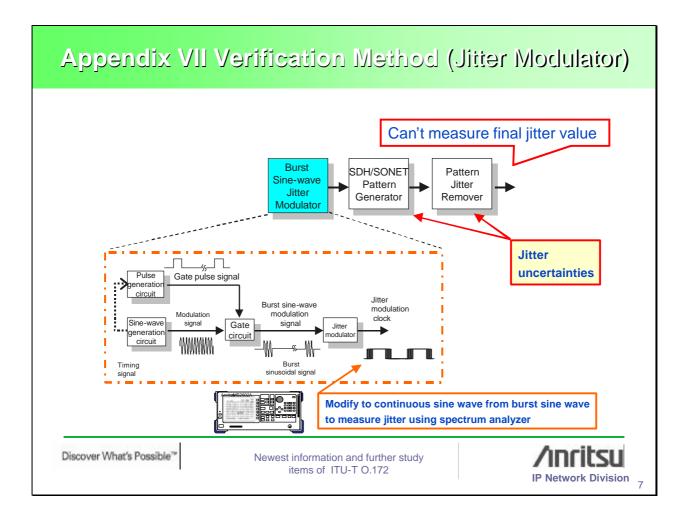

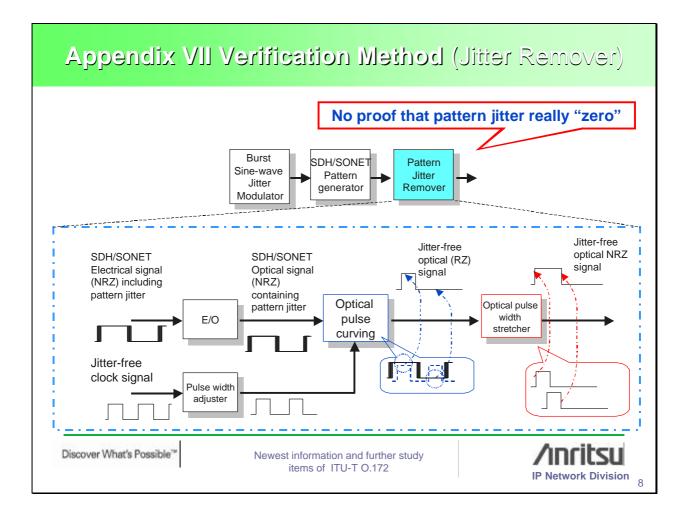

To make the Appendix VII method a practical proposition, it is necessary to produce a reference signal using the three blocks shown here. The block on the left is a jitter modulator that can add jitter of about 100 mUIpp as a burst sinusoidal signal generated at a clock of 9.95328 GHz. The middle block generates an STM-64 (9.95328 Gbit/s) frame signal at a clock of 9.95328 GHz. To obtain the SDH frame signal frame synchronization, a Non Scramble Byte (A1, A2, J0/Z0) is defines at SOH 1ROW. Pattern jitter occurs at this point. In addition, jitter also occurs at the Payload. When a data signal including these jitters is evaluated by the receiver of a jitter tester, accurate jitter evaluation is impossible due to the presence of these jitters. As a consequence, the pattern jitter at the final block shown on the right is used to remove jitter generated in the SDH/SONET pattern, reducing errors due to pattern jitter. However, when evaluating an actual signal, since jitter due to the evaluation-target pattern cannot be completely removed, there is little sense in setting a pattern even if it can be evaluated at various pattern settings (Payload PRBS31 +Scramble).

In this method, since there is no certain way to evaluate the amount of jitter added by the jitter modulated in the final output stage (output of pattern jitter remover), it is not possible to accurately determine the amount of jitter in the evaluation signal. Moreover, since company A has a patent on the block diagram for the pattern jitter remover described in the references, it is necessary to revise the block diagram to a different form so that all users can use the technology free-of-charge without patent licensing issues.

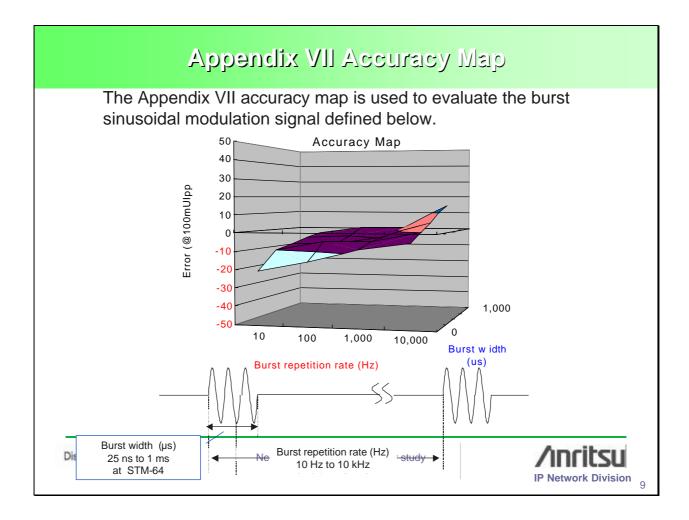

The Appendix VII method performs receiver evaluation with a signal to which jitter is added as a burst sinusoidal wave. However, it is not a method that permits accurate evaluation in the final-stage signal. The Appendix VII method is a method for evaluating whether or not it is possible to detect a fixed peak jitter amount (100 mUlpp) while changing the modulation signal burst repetition rate and burst width. However, Appendix VII provides a method for confirming the amount of added jitter by using a clock signal to which jitter has been added as a continuous sine wave (jitter modulator output) instead of a burst sine wave. In this case, the amount of jitter is found using a spectrum analyzer. In other words, it is possible the perform calibration of the jitter value with a modulation signal having different frequency components from the finally used modulation signal (burst sine wave), based on the supposition that it is the same as the peak jitter value. Moreover, since a signal with a known jitter value is passed through the pattern generator and pattern jitter remover, it is not necessary to take changes in jitter due to these blocks into consideration.

The Appendix VII method requires a pattern jitter remover to remove pattern jitter at 10 mUlpp (1 ps at 10 G) that is a source of error. Unfortunately, there is no method for directly checking jitter of less than 10 mUlpp in the jitter band specified by ITU-T (HP1 + LP).

The Appendix VII method does offer a method for confirming whether or not a fixed peak jitter (100 mUlpp) can be detected at the receiver while varying the modulation signal burst repetition rate and burst width using the matrix shown here. However, this accuracy map evaluation has no meaning when it is not possible to confirm that the amount of jitter generated at the send side under any conditions is constant (100 mUlpp) at the final output.

From here on, I am going to explain some evaluation results produced by Anritsu following the previous meeting in May this year, regarding some issues about the current Appendix VII method, as well as some ideas supporting the current method that do not have accuracy problems. These ideas will be proposed to the next ITU-T meeting.

Now, I will explain the phase analysis technique (O.172 Appendix VIII verification method) for evaluating deterministic jitter such as pattern jitter.

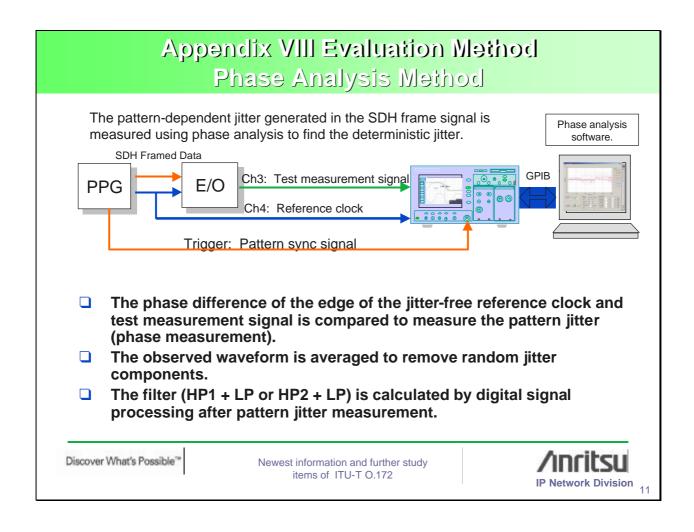

This can be measured using general-purpose measuring instruments. First, an SDH frame signal is generated using a PPG. This signal is converted to an optical signal by an E/O converter and this optical signal is connected to a sampling oscilloscope. The clock for the reference signal is also connected simultaneously and monitored. These signals are synchronized by a pattern sync signal and monitored. Since the reference clock has no pattern jitter, the pattern jitter can be measured by measuring the phase difference of the rising and falling edge of the reference clock and data signal. To eliminate random jitter in this signal and the sampling oscilloscope itself, the signal is averaged using the averaging function and then evaluated. The jitter filtering required to evaluate jitter is performed by filter processing using DSP after the phase difference data has been completely measured.

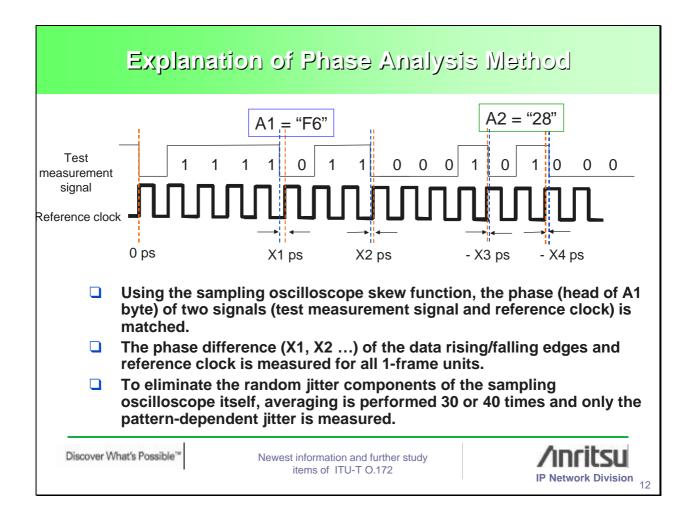

Here is a slightly more concrete explanation. This diagram shows the test measurement signal data and reference clock. First, the skew function of the sampling oscilloscope is used to align the edge of the A1 byte of the non scramble byte. Next, the phase difference X1 ps between the data edge (here only the falling edge is monitored but actually both the rising and falling edges are monitored) and the reference clock is measured. The phase difference (X2, X3, ...) between each edge and the reference clock is measured for every frame while the signal drifts. (It is also possible to measure the scramble byte part.) As explained before, the phase analysis technique separates out only deterministic jitter for evaluation so random jitter is removed by the averaging function. Since this measurement is a relative evaluation of the clock and data, sampling oscilloscope error can be ignored.

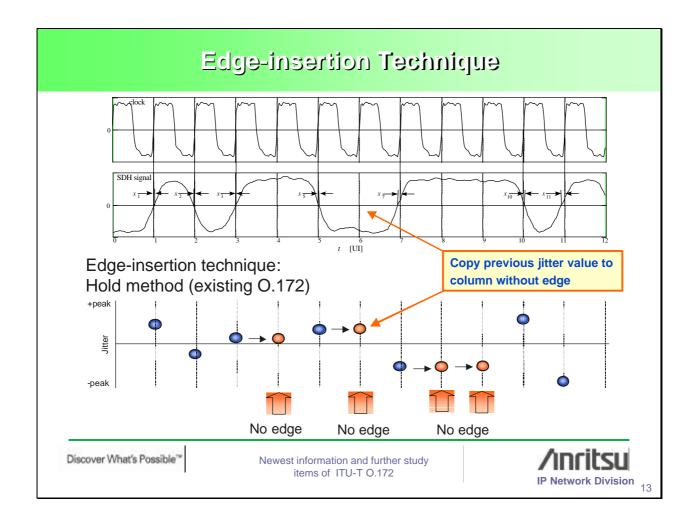

Appendix VIII describes use of a sampling oscilloscope to evaluate the amount of jitter in a data signal. The phase difference at the edge of the data signal and the reference clock signal is measured at each bit using a sampling oscilloscope to find the pattern jitter of the data signal without using a jitter tester as the measuring instrument. At the May 2004 meeting, the need for technical support for an interpolation method for NRZ data with no edge was identified but could not be evaluated due to time considerations. The following materials explain the various edge-insertion techniques that our company has investigated following the ITU-T meeting that do not present the accuracy problems of the current Hold method.

The figure in this slide shows a comparison of the phase difference (blue) of the edges of the clock and data signals, indicating the points (orange) where the jitter value of previous edge was copied because there was no edge so as specified in Appendix VIII.

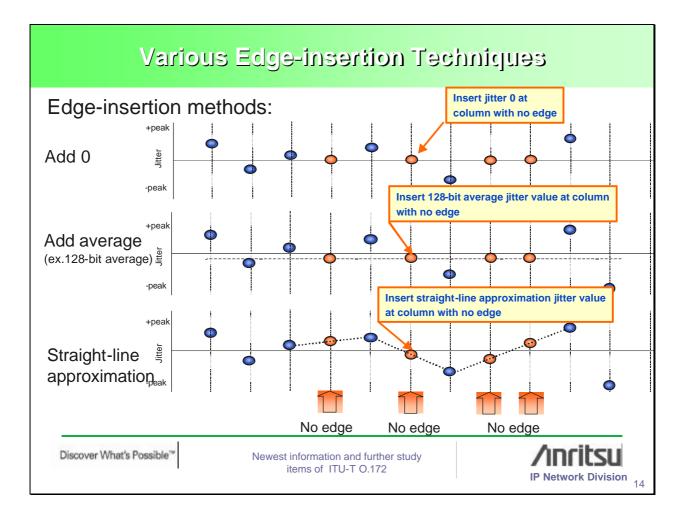

Another two other methods were proposed at the previous ITU-T meeting in addition to the Hold method described on the previous slide. The top part of this slide shows the Add 0 method in which a jitter value of 0 is added at parts where there is no edge. The middle part shows the Add average method in which the average jitter value for the previous 128 bits is added to the parts where there is no edge. However, neither of these two methods was proposed based on any evidence of real technical advantages. The bottom part of this slide shows the method examined by Anritsu; in this method, a straight line is approximated between the previous and succeeding edges and the interpolated value is inserted at the point where there is no edge. These four methods were simulated to examine the error inherent in each method.

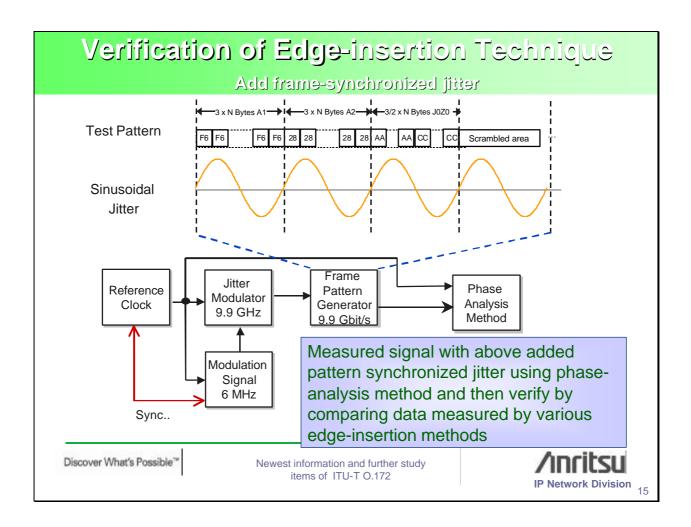

To investigate the edge-insertion error, it is necessary to specify the theoretical value. As shown in this block diagram, evaluation was performed by simulating a signal to which jitter is added using a sinusoidal modulation waveform synchronized to the SDH frame. In other words, the block diagram shown here is not the block diagram used for the actual evaluation—it only shows a conceptual image of the evaluation system. First, an SDH frame pattern with no pattern jitter is generated by a simulator. Since the signal is produced by a simulator, all the jitter values are zero. A phase variation is produced by the synchronization of the modulation signal (sine wave or burst wave with this generated pattern. This makes it possible to find the phase error of each edge of a signal to which hypothetical phase variation has been added using a simulator in the same manner as Appendix VIII. In this case, we measured and compared the jitter value at the points with no edge in the previously described four methods.

As explained before, phase modulation is caused by the modulation signal synchronized to the pattern so we can determine the theoretical value of the jitter even at locations with no edge and this was used to evaluate the errors of each edge-insertion method.

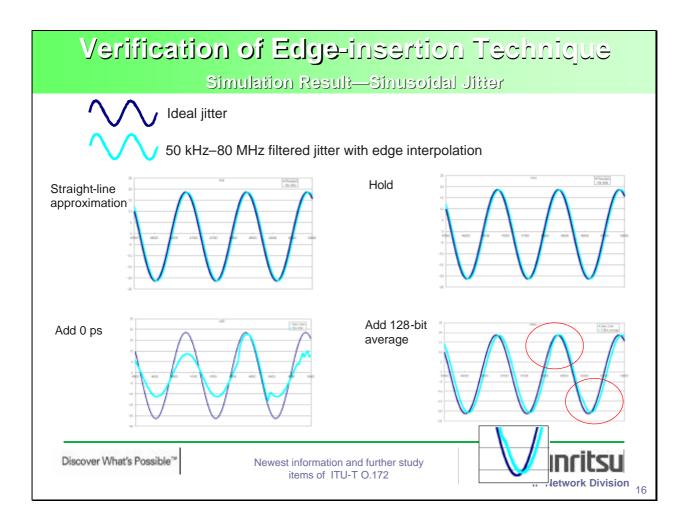

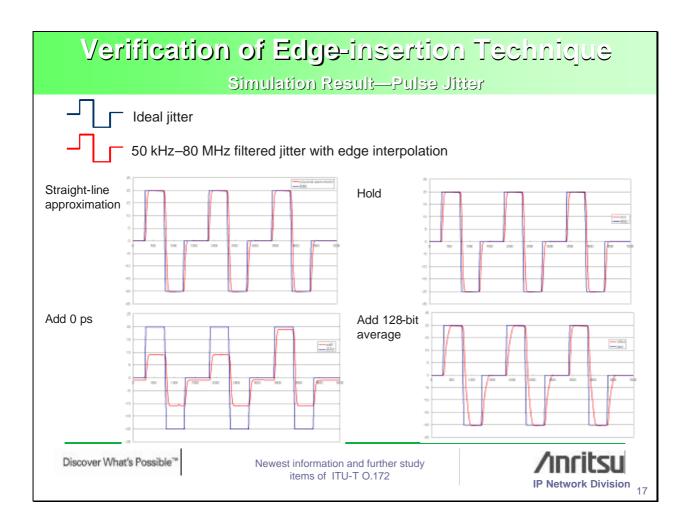

This slide shows the measured phase errors obtained by comparing the results obtained by the methods in Appendix VIII and the ideal results obtained by simulation. In this case, a sine wave was used as the modulation signal because the aim was to confirm the degree of distortion caused by each edge-insertion method. The dark blue line is the ideal jitter while the light blue line shows the results found for each of the interpolation methods.

As you can see, the Hold method specified in Appendix VIII and the new straight-line approximation method examined by Anritsu produce very similar results with almost the same values and little jitter. On the other hand, the Add 0 method produces unquestionable jitter. In addition, the Add 128 bit average method causes some jitter (and the same trend even with a different bit count).

Instead of using a sine-wave modulation signal, the next slide compares the frame-pattern simulated pulse jitter. The dark blue line shows the ideal jitter and the red line shows the result for each interpolation method. The results of the Hold method specified in Appendix VIII and the new straight-line approximation method evaluated by Anritsu are very similar with practically no delay other than delay caused by the 80-MHz LPF and very similar jitter values. On the other hand, the Add 0 insertion method produces unquestionable jitter. In addition, the Add 128 bit average method causes large delay other than delay caused by the 80-MHz LPF and some jitter (and the same trend even with a different bit count).

## Verification of Edge-insertion Technique Edge Insertion—Simulation Summary

|                         | Pattern-dependent jitter waveform |           |           |           |  |  |  |  |

|-------------------------|-----------------------------------|-----------|-----------|-----------|--|--|--|--|

| Internelation           | Sine v                            | wave      | Rectangu  | ular wave |  |  |  |  |

| Interpolation<br>method | Peak-Peak                         | RMS       | Peak-Peak | RMS       |  |  |  |  |

|                         | Error [%]                         | Error [%] | Error [%] | Error [%] |  |  |  |  |

| Hold                    | -1                                | 0         | -2        | -1        |  |  |  |  |

| Null                    | -20                               | -46       | -30       | -47       |  |  |  |  |

| 128-bit average         | -4                                | -4        | -1.8      | -6        |  |  |  |  |

| Straight-line           | -0.1                              | 0         | -0.5      | -0.8      |  |  |  |  |

➤The accuracy of the edge-insertion technique can be confirmed by inspecting the jitter imposed by a pattern-synchronized sinewave modulation signal and a pulse-modulation signal.

Clearly both the 0-ps and averaged-value approaches are inadequate for accurate measurement.

The most accurate results are derived by using the Hold or Straight-line Approximation methods (small distortion).

```

Discover What's Possible™

```

Newest information and further study items of ITU-T 0.172

This table summarizes the simulation results explained so far; for the Hold edge-insertion method specified in Appendix VIII, the difference between the ideal jitter value and the jitter value at sine-wave modulation was just -1% and was -2% at pulse wave modulation. On the other hand for the Add 0 method proposed at the previous meeting, the same errors were extremely large at -20% and -30%, respectively. For the Add 128-bit average method, the error was -4% at sine-wave modulation and -18% at pulse wave modulation.

From these results, it is clear that the currently recommended Hold edge-insertion method has no serious problems in terms of accuracy. However, it is also clear that the newly examined straight-line approximation method also produces even smaller errors than the Hold method.

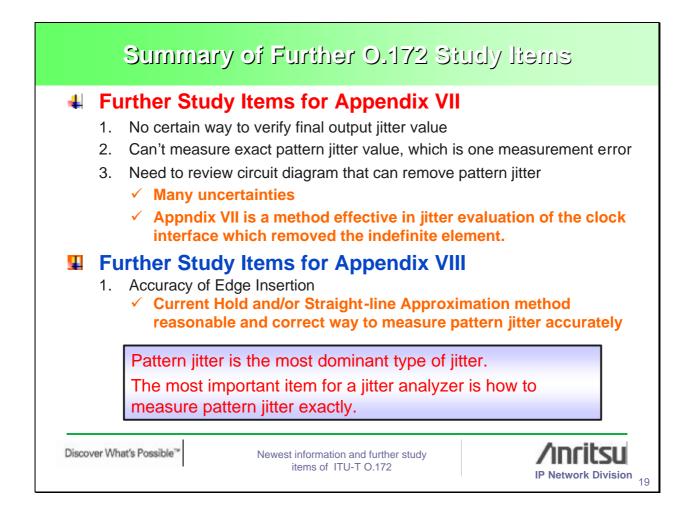

This slide summarizes all the issues discussed so far.

For the Appendix VII method:

First, the fatal problem is that since there is no certain way to versify the jitter value in the final output, there is no way to obtain the traceability needed for assuring accuracy.

Second, since it is not possible to verify the existence or degree of pattern jitter (10 mUlpp), accuracy will always be limited by addition of this error.

Third, Appendix VII is a method effective in jitter evaluation of the clock interface which removed the indefinite element.

For the Appendix VIII method:

First, our simulation results confirm that the current Hold method has no problems with accuracy.

Second, at evaluation of an actual signal, the most important consideration is to use a method that is able to accurately evaluate the pattern jitter, which is the most serious jitter included in the signal.

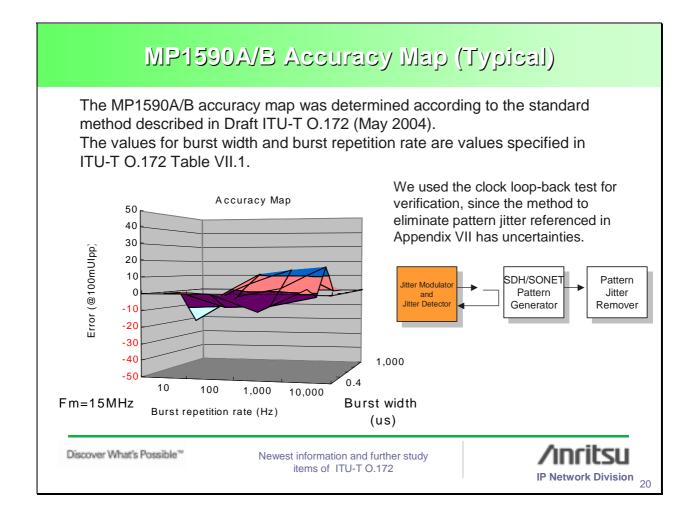

This slide shows some typical measurement results when the MP1590A/B is evaluated using the evaluation system of Appendix VII. We can see that the randomness is excellent and within  $\pm 15$  mUlpp. This evaluation was performed by looping back a calibrated clock signal to eliminate the above-described accuracy issues.

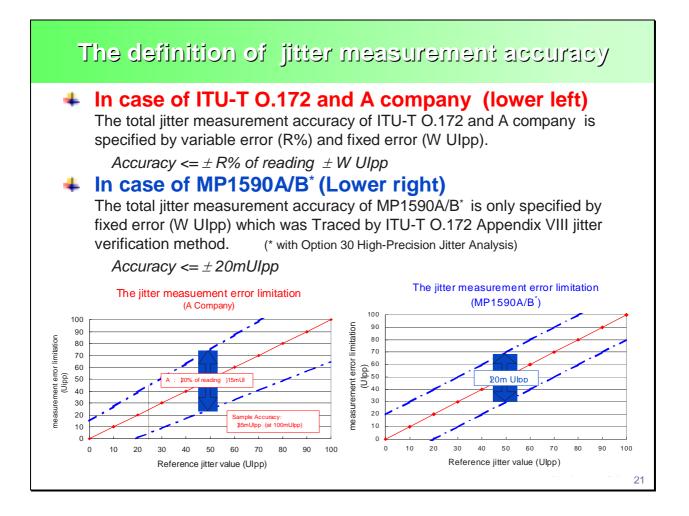

This slide explains some definition of jitter measurement accuracy. In case of ITU-T O.172 and A company, the total jitter measurement accuracy of ITU-T O.172 and A company is specified by variable error (R%) and fixed error (W Ulpp) as following formula.

In case of ITU-T O.172 and A company, the total jitter measurement accuracy is specified by variable error (R%) and fixed error (W UIpp) as following formula.

Accuracy  $\leq \pm R\%$  of reading  $\pm W$  Ulpp

Blue line on the figure show the maximum error . In case of ITU-T O.172, the maximum measurement error is  $\pm$  55mUlpp to reference jitter value 100mUlpp. In case of A Company, the maximum measurement error  $\pm$  35mUlpp to reference jitter value 100mUlpp.

The total jitter measurement accuracy of MP1590A/B<sup>\*</sup> is only specified by fixed error (± 20mUlpp) which was traced by ITU-T O.172 Appendix VIII jitter verification method. You can see to compare two figures which is better.

|                                                                                                      | Compai                                   | ٢j | son Ta                                                                               | ble  |                                                                              |               |

|------------------------------------------------------------------------------------------------------|------------------------------------------|----|--------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------|---------------|

| Specifications                                                                                       | ITU-T 0.172                              |    | Analyzer A                                                                           |      | Anritsu                                                                      |               |

| Bit Rate                                                                                             | -                                        |    | 10G                                                                                  |      | 2.5G/10G                                                                     |               |

| Errors                                                                                               | ±R% ±35 mUI                              |    | ±R% ±15 mUI<br>Against Jitter except pattern jitter<br>based on Appendix-VII method. |      | ±20 mUI<br>Against standardized transmitter<br>total by Appendix-VIII method |               |

| Generation Meas.<br>Repeatability                                                                    | -                                        |    | not specify                                                                          |      | ±5 mUI<br>Specified in data sheet                                            |               |

| Subject of Jitter<br>verification                                                                    | -                                        |    | Burst sine-wave Jitter                                                               |      | DJ + RJ                                                                      |               |

| Calibration Point                                                                                    | Appendix VII<br>Appendix VIII            |    | Accuracy map<br>under the Burst sine-wave Jitter                                     |      | Two or more Golden Tx<br>(PJ at each Tx are different.)                      |               |

| Optical Input Power                                                                                  | -10 to -12 dBm                           |    | -6 to -10 dBm<br>Not conform to ITU-T Spec.                                          |      | -10 to -12 dBm<br>Conforms to ITU-T Spec.                                    |               |

| Optical Wavelength                                                                                   | -                                        |    | 1.55 µm                                                                              |      | 1.31/1.55 μm                                                                 |               |

| Payload Test Pattern                                                                                 | PRBS23, PRBS31<br>All 0s (Appendix VIII) |    | PRBS31                                                                               |      | All 0s (Appendix VIII)                                                       |               |

|                                                                                                      |                                          | _  |                                                                                      | R    | fm (Hz)                                                                      | ]             |

| Example: Maximum error referred to<br>expected value of 50 mUlpp<br>±20% of 50 mUl ±15 mUl = ±25 mUl |                                          |    |                                                                                      | ±7%  | 20 – 300 kHz                                                                 |               |

|                                                                                                      |                                          | ł  |                                                                                      | ±8%  | 300 kHz – 1 MHz                                                              |               |

|                                                                                                      |                                          |    | n and further stu                                                                    | ±10% | 1 – 3 MHz                                                                    | hritsu        |

|                                                                                                      | items of                                 | П  | TU-T 0.172                                                                           | ±15% | 3 – 10 MHz                                                                   | work Division |

|                                                                                                      |                                          |    |                                                                                      | ±20% | 10 – 80 MHz                                                                  | WORK DIVISION |

Lastly, this table compares the measurement accuracy specified by ITU-T O.172 and that provided by Anritsu's MP1590A/B and another analyzer.

First, the MP1590A/B supports both bit rates of 2.5 and 10G but the other analyzer only supports 10 G. This is important for assuring traceability even for the many direct modulators operating at 2.5 G. (By following Appendix VIII, Anritsu can assure traceability for direct modulators.)

Second, although error is defined, with the Anritsu equipment we are able to assure an error of  $\pm 20$  mUlpp referenced to a transmitter standardized by the Appendix VIII method. By comparison, the other analyzer assures an accuracy of  $\pm 15$  mUlpp based on the uncertain traceability of Appendix VII. As shown below, since this includes the ITU-T 0.172 modulation frequency error, the true error specification is actually  $\pm R\%$  (up to 20%)  $\pm 15$  mUl. Moreover, Anritsu are able to assure an repeatability error of  $\pm 5$ mUlpp. The other analyzer does not have such specification.

Third, the MP1590A/B are able to assure as total jitter value which include DJ (Deterministic Jitter) and RJ (Random Jitter). Moreover, MP1590A/B is calibrated by some different transmitters standardized by the Appendix VIII method. The another analyzer only assure burst sinusoidal jitter value.

|                                                                                                      | Compar                                   | ʻj | son Is                                                                               | ble  |                                                                              |               |

|------------------------------------------------------------------------------------------------------|------------------------------------------|----|--------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------|---------------|

| Specifications                                                                                       | ITU-T 0.172                              |    | Analyzer A Anritsu                                                                   |      |                                                                              | su            |

| Bit Rate                                                                                             | -                                        |    | 10G                                                                                  |      | 2.5G/10G                                                                     |               |

| Errors                                                                                               | ±R% ±35 mUI                              |    | ±R% ±15 mUI<br>Against Jitter except pattern jitter<br>based on Appendix-VII method. |      | ±20 mUI<br>Against standardized transmitter<br>total by Appendix-VIII method |               |

| Generation Meas.<br>Repeatability                                                                    | -                                        |    | not specify                                                                          |      | ±5 mUI<br>Specified in data sheet                                            |               |

| Subject of Jitter<br>verification                                                                    | -                                        |    | Burst sine-wave Jitter                                                               |      | DJ + RJ                                                                      |               |

| Calibration Point                                                                                    | Appendix VII<br>Appendix VIII            |    | Accuracy map<br>under the Burst sine-wave Jitter                                     |      | Two or more Golden Tx<br>(PJ at each Tx are different.)                      |               |

| Optical Input Power                                                                                  | -10 to -12 dBm                           |    | -6 to -10 dBm<br>Not conform to ITU-T Spec.                                          |      | -10 to -12<br>Conforms to ITU                                                |               |

| Optical Wavelength                                                                                   | -                                        |    | 1.55 µm                                                                              |      | 1.31/1.55                                                                    | 5 μm          |

| Payload Test Pattern                                                                                 | PRBS23, PRBS31<br>All 0s (Appendix VIII) |    | PRBS31                                                                               |      | All 0s (Apper                                                                | ndix VIII)    |

|                                                                                                      |                                          | -  |                                                                                      | R    | fm (Hz)                                                                      | ]             |

| Example: Maximum error referred to<br>expected value of 50 mUlpp<br>±20% of 50 mUl ±15 mUl = ±25 mUl |                                          |    |                                                                                      | ±7%  | 20 – 300 kHz                                                                 |               |

|                                                                                                      |                                          | ŀ  |                                                                                      | ±8%  | 300 kHz – 1 MHz                                                              |               |

|                                                                                                      |                                          |    | n and further stu                                                                    | ±10% | 1 – 3 MHz                                                                    | nritsu        |

|                                                                                                      | items of IT                              |    |                                                                                      | ±15% | 3 – 10 MHz                                                                   | work Division |

|                                                                                                      |                                          |    |                                                                                      | ±20% | 10 – 80 MHz                                                                  |               |

Fourth, the optical level for assuring accuracy specified by ITU-T O.172 should cover a range of -10 to -12 dBm for all optical interfaces recommended by ITU-T G series Anritsu's MP1590A/B completely satisfies this specification. Additionally, there is hardly any level dependence even outside this level range. The other analyzer does not conform to the range specified by 0.172 and does not conform to the optical interfaces recommended by ITU-T G series.

Fifth, the MP1590A/B supports both wavelengths of 1.31 and 1.55  $\mu$ m while the other analyzer only supports 1.55  $\mu$ m.

sixth, for the payload test pattern, Anritsu's MP1590A/B supports the pattern specified by Appendix VII/A.1 of ITU-T O.172, whereas the other analyzer supports PRBS2<sup>31</sup>-1. As explained in the notes on Slide 9, although company A's specification is based on Appendix VII A, since evaluation is performed with a signal from which pattern-dependent jitter has been completely removed and to which burst sine-wave jitter has been added, the guaranteed generation pattern has no meaning.

To offer a more complete understanding of the issues we have discussed here today, we are planning to publish more of these types of reference materials after the next ITU-T meeting.

Thank you.

#### ANRITSU CORPORATION

1800 Onna, Atsugi-shi, Kanagawa, 243-8555 Japan Phone: +81-46-223-1111 Fax: +81-46-296-1264

#### • U.S.A.

ANRITSU COMPANY TX OFFICE SALES AND SERVICE 1155 East Collins Blvd., Richardson, TX 75081, U.S.A. Toll Free: 1-800-ANRITSU (267-4878)

Phone: 1-972-644-777

Fax: +1-972-644-3416

Canada

**ANRITSU ELECTRONICS LTD.** 700 Silver Seven Road, Suite 120, Kanata, ON K2V 1C3, Canada Phone: +1-613-591-2003 Fax: +1-613-591-1006

#### • Brasil ANRITSU ELETRÔNICA LTDA.

Praca Amadeu Amaral, 27 - 1 andar 01327-010 - Paraiso, Sao Paulo, Brazil Phone: +55-11-3283-2511 Fax: +55-11-3886940

• U.K.

ANRITSU LTD. 200 Capability Green, Luton, Bedfordshire LU1 3LU, U.K. Phone: +44-1582-433280 Fax: +44-1582-731303

### Germany ANRITSU GmbH

Grafenberger Allee 54-56, 40237 Düsseldorf, Germany Phone: +49-211-96855-0 Fax: +49-211-96855-55

France

ANRITSU S.A.

9, Avenue du Québec Z.A. de Courtabœuf 91951 Les

Ulis Cedex, France

Phone: +33-1-60-92-15-50

Fax: +33-1-64-46-10-65

Italy

ANRITSU S.p.A. Via Elio Vittorini, 129, 00144 Roma EUR, Italy Phone: +39-06-509-9711 Fax: +39-06-502-2425

Sweden

ANRITSU AB

Borgafjordsgatan 13 164 40 Kista, Sweden Phone: +46-853470700 Fax: +46-853470730

• Singapore

ANRITSU PTE LTD. 10, Hoe Chiang Road #07-01/02, Keppel Towers, Singapore 089315 Phone: +65-6282-2400 Fax: +65-6282-2533 Specifications are subject to change without notice.

#### Hong Kong

ANRITŠU COMPANY LTD. Suite 923, 9/F., Chinachem Golden Plaza, 77 Mody Road, Tsimshatsui East, Kowloon, Hong Kong, China Phone: +852-2301-4980 Fax: +852-2301-3545

• P. R. China ANRITSU COMPANY LTD.

### Beijing Representative Office

Room 1515, Beijing Fortune Building, No. 5 North Road, the East 3rd Ring Road, Chao-Yang District Beijing 100004, P.R. China Phone: +86-10-6590-9230

Korea

ANRITSU CORPORATION

8F Hyun Juk Bldg. 832-41, Yeoksam-dong, Kangnam-ku, Seoul, 135-080, Korea Phone: +82-2-553-6603

Phone: +82-2-553-6603 Fax: +82-2-553-6604 • Australia

ANRITSU PTY LTD.

Unit 3/170 Forster Road Mt. Waverley, Victoria, 3149, Australia Phone: +61-3-9558-8177 Fax: +61-3-9558-8255

Taiwan

ANRITSU COMPANY INC. 7F, No. 316, Sec. 1, NeiHu Rd., Taipei, Taiwan Phone: +886-2-8751-1816 Fax: +886-2-8751-1817

040602

No.MP1590jitter-E-E-1-(2.00) An Printed in Japan 2004-12 AKD