高速シリアルバス インタフェースソリューション PCIe 5サポート

シグナル クオリティ アナライザ-R MP1900Aシリーズ

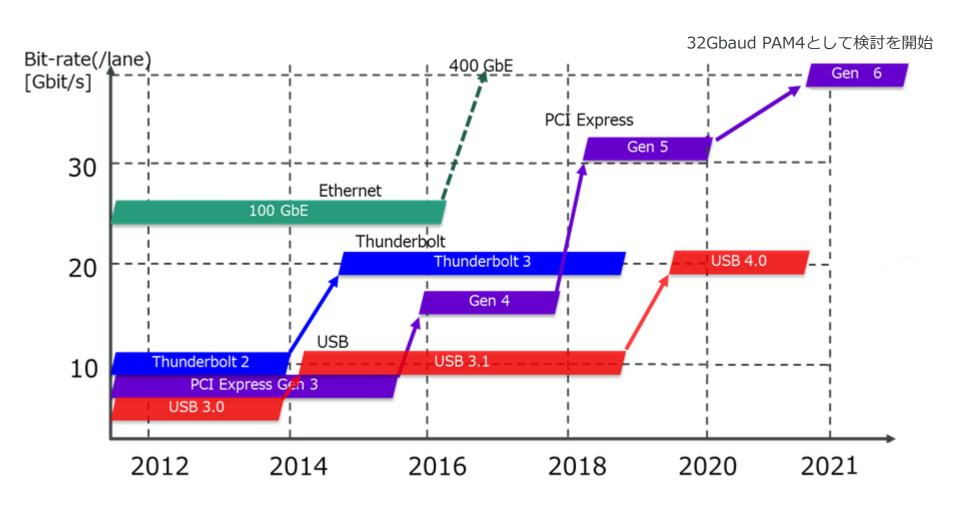

### PCIe、USB、Thunderbolt市場のトレンド

### 主要機能

PCIe-G4/G5

PAM4

**AOC** 光トランシーバ

Network IFからBUS IFまでを1台でサポート

#### ・ シグナルクオリティ

- 低ジッタ/クリーンアイ

- Tx向け10タップエンファシス

- 高感度

- Rx向け12 dB可変CTLE

- ジッタ/ノイズ発生源を1台に

#### ・拡張性

- 32 Gbit/s 、最大16chのNRZ

- 112 Gbit/s、最大4chのPAM4(56 Gbaud)

#### 解析能力

- PCIe-G5ビットレート(32G NRZ)に対応

- PCIe-G5 リンクトレーニング (ネゴシエーション)

- PCIe-G5 LTSSM解析

- FECパターン生成

#### 使いやすさ

- オールインワン: PC コントローラ、ノイズ 発生源、エンファシス、CTLE、CDRなど

- 新しいGUI/タッチスクリーン

### MP1900Aシリーズ製品

- 複数インタフェースをサポートする高拡張性ソフトウェアソリューション

- デバイスのRxテストキャリブレーションおよびテスト自動化

| モデル                                | 型名・品名                    | オプション                               | 注記          |  |  |  |

|------------------------------------|--------------------------|-------------------------------------|-------------|--|--|--|

| MP1900A                            | シグナル クオリティ アナライザ-R       |                                     |             |  |  |  |

| MU181000B                          | 12.5GHz 4ポート シンセサイザ      | 02                                  |             |  |  |  |

| MU181500B                          | ジッタ変調源                   |                                     |             |  |  |  |

| MU195020A                          | 21G/32G bit/s SI PPG     | 01, 10, 11, 40 or<br>01, 20, 21, 41 | 1chまたは2ch   |  |  |  |

| MU195040A                          | 21G/32G bit/s SI ED      | 01, 10, 11, 22                      | 1ch         |  |  |  |

| MU195050A                          | ノイズジェネレータ                |                                     |             |  |  |  |

| MX183000A-PL001                    | ジッタトレランステストソフトウェア        |                                     |             |  |  |  |

| MX183000A-PL021                    | PCIeリンクトレーニングソフトウェア      |                                     |             |  |  |  |

| MX183000A-PL025                    | PCIe Gen5リンクトレーニングソフトウェア |                                     | New release |  |  |  |

| Keysight/Tektronix Scope用自動化ソフトウェア |                          |                                     |             |  |  |  |

| GRL-PCIE4-BASE-RXA                 | PCIE Gen4 Base自動化ソフトウェア  |                                     |             |  |  |  |

| GRL-PCIE4-CEM-RXA                  | PCIE Gen4 CEM 自動化ソフトウェア  |                                     |             |  |  |  |

| GRL-PCIE5-BASE-RXA                 | PCIE Gen5 Base 自動化ソフトウェア |                                     |             |  |  |  |

| GRL-PCIE5-CEM-RXA                  | PCIE Gen5 CEM 自動化ソフトウェア  |                                     | New release |  |  |  |

| Teledyne Lecroy Scope用自動化ソフトウェア    |                          |                                     |             |  |  |  |

| QPHY-PCIE-Tx-Rx                    | PCIE Gen3/4/5自動化ソフトウェア   |                                     | *           |  |  |  |

\*1: Gen5 CEMのサポートについてはお問い合わせください

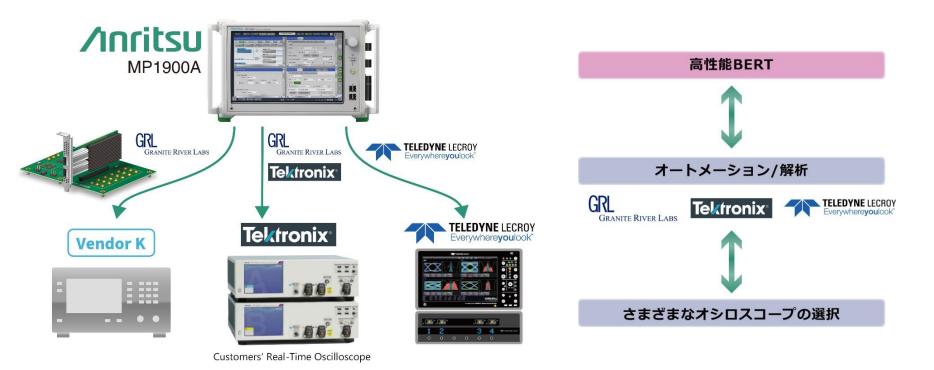

### PCIe Tx LEQ/Rxコンプライアンステスト

- 最高性能のBERT MP1900Aと推奨オシロスコープの組み合わせ -

#### 試験時間の短縮と投資費用の低減

- ➤ Lecroy/Tektronix/Keysightリアルタイムオシロスコープとの組み合わせをサポート

- ▶ 自動化されたRx CEMおよびBase Test: キャリブレーション、Link EQおよび自動化されたTxテスト

- プロトコルアウェア:リンクトレーニング/イコライゼーションおよびLTSSM解析

- ▶ PCIe1~5に対応する高拡張性32GマルチチャネルBERT

# PCIe Gen5テストソリューション

### PCI Express Gen5 Rxテスト機能

#### ✓ 主要機能

- 自動化ソフトウェアを使用した自動測定およびキャリブレーション GRL-PCIE5-BASE/CEM-RXA/QPHY-PCIE-Tx-Rx

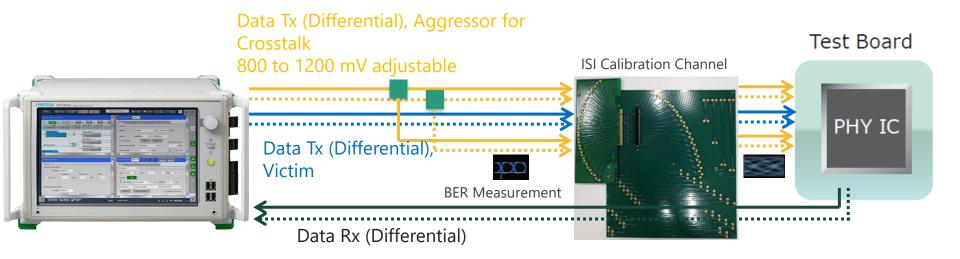

- デュアルチャネルPPGを使用した真のクロストークテスト

- MX183000Aを使用した論理サブブロックの評価

#### サポートする規格

| サポートする規格              | i e                     | DUT キャリブレーション             |                          | リンクトレーニング      | ジッタトレランステスト |  |

|-----------------------|-------------------------|---------------------------|--------------------------|----------------|-------------|--|

| PCI Express<br>Base規格 | 1.x/2.0/3.x/<br>4.0/5.0 | ホスト/<br>エンドポイント<br>SERDES | 3.x/4.0/5.0:<br>サポート     | 1.0~4.0 : サポート | サポート        |  |

| PCI Express<br>CEM規格  | 3.x/4.0/5.0             | システム/<br>デバイスカード          | 3.x/4.0:サポート<br>5.0:サポート | 5.0:サポート       |             |  |

#### ジッタトレランステスト機能 (Opt-PL001)

- ✓ SJ/RJの印可によるPHYデバイスのジッタ トレランステスト

- ✓ 低レート推定BER測定を使用したデバイス マージンテスト

- ✓ HTMLおよびCSVフォーマットでの測定結果 レポート作成

### Anritsu PCIeソリューションの機能(1/2)

### 主な自動化ソフトウェア機能 GRL-PCIE5-BASE/CEM-RXA/QPHY-PCIE-Tx-Rx

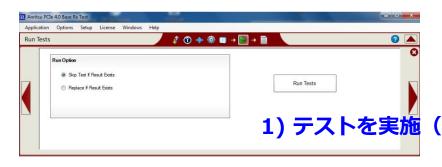

PCIe 5.0 Rx Base/CEM Spec Baseの完全に自動化された波形 キャリブレーション

容易なRxストレストレランステスト

自動キャリブレーションが試験条件の分散を制御(散発/ランダム)

一貫したテスト結果が得られる高速波形キャリブレーション

### MX183000Aの主要な機能

PCIe Gen1~Gen5のループバックモード ジッタトレランスマージンテスト

### アプリケーション規格

- データレート: 32 GT/s

- コモン/SRIS/SRNSクロックアーキテクチャ

- 必要な機器:

- Keysight 50 GHzオシロスコープ(DSAX またはそれ以降のシリーズ)または

Tektronix 50 GHz(DPSまたはそれ以降のシリーズ)

- アンリツ シグナル クオリティ アナライザ-R MP1900A

- Gen5 Base FixtureまたはGen4 ISI Board

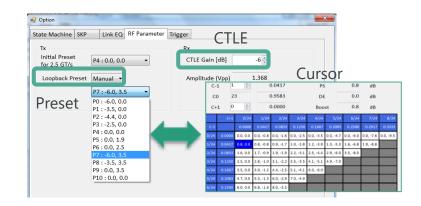

### Anritsu PCIeソリューションの機能(2/2)

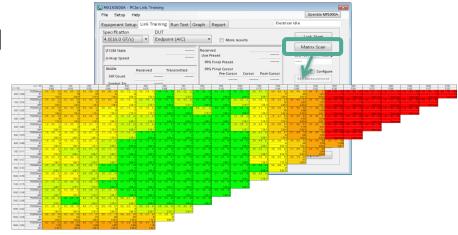

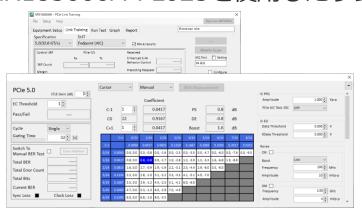

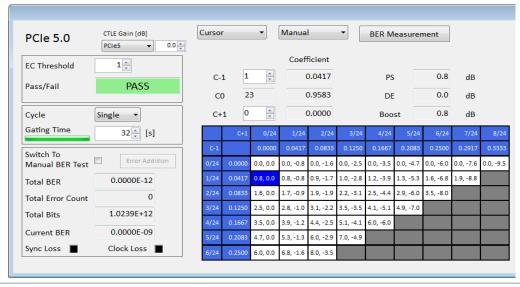

### ビットエラー解析

- ▶ ループバックプリセットをマニュアルに設定し、プリセットをPO からP10に変更して、DUTにおける最適なプリセット/カーソルを決定します。

- ▶ DUTの最適な設定を見つけるには、 CTLEゲインを0から12 dBに変更 します。

- マトリックススキャン機能を使用 すれば、最適なTx EQ値を自動で 見つけることができます。

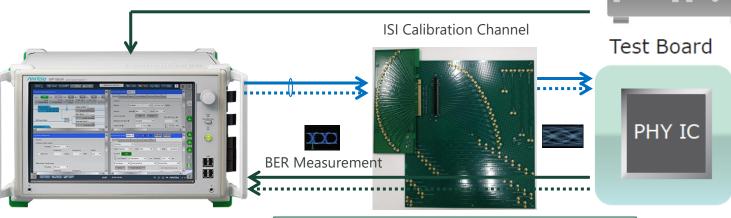

### MP1900Aを使用したRxテストおよびBER測定のためのストレス信号生成

#### ▶ ストレス信号の生成

・ジッタ付加機能:SJ/RJ/SSC

・ノイズ付加機能:コモンモード/差動モード

・エンファシス制御

・クロストーク信号生成:マルチチャネル最大4ch/MP1900A

#### **▶** BER測定

・ジッタトレランス測定

・高感度入力機能:15 mV(typ.) アイ高さ入力

・CDR機能: 2.4~32.1 Gbit/s 広帯域

・内蔵CTLE: 0~12 dB/0.1 dB

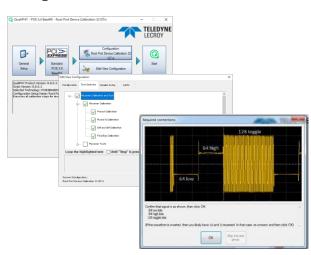

キャリブレーションのための 自動化ソフトウェア

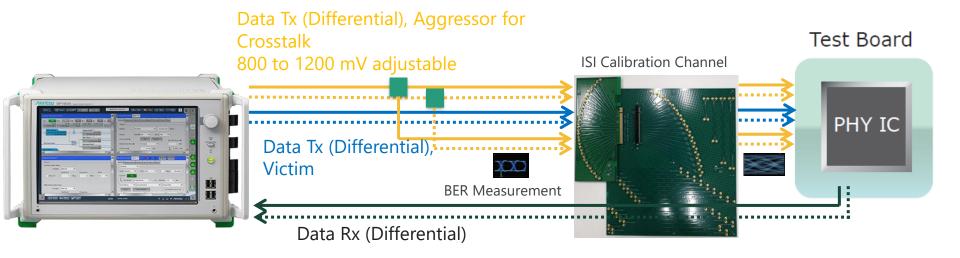

### Gen5クロストークテスト

• デュアルチャネルPPGが真のクロストークテストを可能にします。

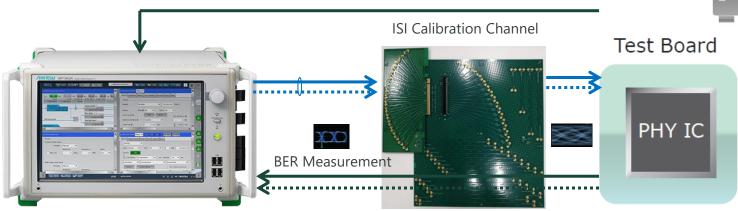

### PCI Express Gen5 Rxテストの概要

➤ PCI Express PHY IPデバイスRxテストの流れ

#### ストレス信号 キャリブレーション

#### ループバック ステータスへの移行

自動化ソフトウェア:

GRL-PCIE5-BASE/CEM-RXA ソフトウェア:

または

適用可能な

**OPHY-PCIE-Tx-Rx**

リンクトレーニング

MX183000A-PL021 (Gen1~4)

MX183000A-PL025 (Gen5)

#### ストレス信号 入力テスト

・ジッタトレランスマージンテスト:

MX183000A-PL001

または

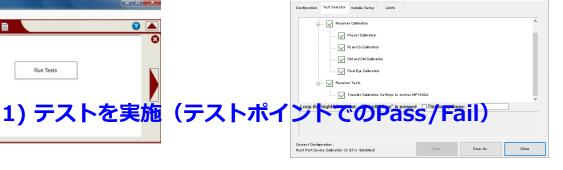

・ジッタSweepテスト(Pass/Fail):

GRL-PCIE5-BASE/CEM-RXA または

QPHY-PCIE-Tx-Rx

キャリブレーションのための 自動化ソフトウェア

PCI express測定の概要

# PCI Express Gen5キャリブレーションポイント(1/3)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 <u>入力</u>テスト

|                        |                             |                | Table 8-9 Stre             | essed Jitter Eye         | Parameters               |                          |        |                                                   |

|------------------------|-----------------------------|----------------|----------------------------|--------------------------|--------------------------|--------------------------|--------|---------------------------------------------------|

| Symbol                 | Parameter                   | 2.5 GT/<br>s   | 5.0 GT/s                   | 8.0 GT/s                 | 16.0 GT/s                | 32.0 GT/s                | Units  | Details                                           |

| V <sub>RX-LAUNCH</sub> | Generator<br>launch voltage | 800 to<br>1200 | 800 to 1200                | 800 to 1200              | 720 to 800               | 720 to 800               | mV PP  | Note 1                                            |

| T <sub>RX-UI</sub>     | Unit Interval               | 400            | 200                        | 125                      | 62.5                     | 31.25                    | ps     |                                                   |

| T <sub>RX-ST</sub>     | Eye width                   | ≤ 0.4          | ≤ 0.32                     | ≤ 0.30                   | ≤ 0.30                   | ≤ 0.30                   | UI     | Note 3, 4, 8,                                     |

| V <sub>RX-ST</sub>     | Eye height                  | ≤ 175          | ≤ 100                      | ≤ 25                     | ≤ 15                     | ≤ 15                     | mV PP  | Note 2, 4, 8, 9                                   |

| T <sub>RX-ST-SJ</sub>  | Swept Sj                    | N/A            | 75 ps (max)<br>See Note 11 | See Section<br>8.4.2.2.1 | See Section<br>8.4.2.2.1 | See Section<br>8.4.2.2.1 | ps     | Note 5                                            |

| T <sub>RX-ST-RJ</sub>  | Random Jitter               | N/A            | 3.4                        | (max)<br>3.0             | 1.0                      | 0.5                      | ps RMS | Note 6, 7                                         |

| VRX-DIFF-INT           | Differential<br>noise       | N/A            | N/A                        | 14                       | 14                       | 10                       | mV PP  | Note 7, 12 Adjust to set EH. Frequency = 2.1 GHz. |

| V <sub>RX-CM-INT</sub> | Common mode noise           | 150            | 150                        | 150                      | 150                      | 150                      | mV PP  | Note 8                                            |

# PCI Express Gen5キャリブレーションポイント(2/3)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 <u>入力</u>テスト

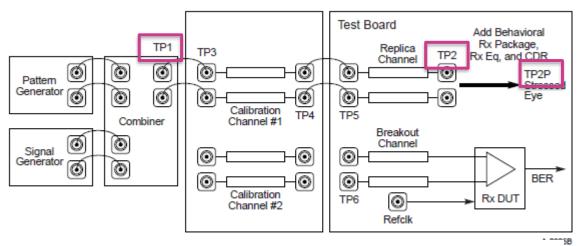

Figure 8-22 Rx Testboard Topology for 16.0 and 32.0 GT/s

**MP1900A**

# PCI Express Gen5キャリブレーションポイント(3/3)

### ストレス信号 キャリブレーション

ループバック ステータスへの移行 ストレス信号 <u>入力テ</u>スト

▶ ストレス信号キャリブレーション

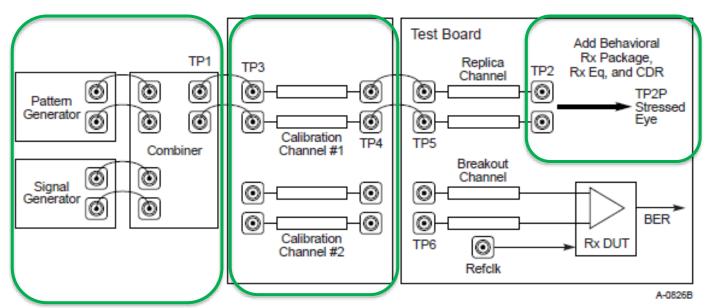

自動化ソフトウェアGRL-PCIE5-BASE/CEM-RXA/QPHY-PCIE-Tx-Rx機能

キャリブレーションの設定および測定画面の例

自動化ソフトウェアを使用したストレス入力信号のワンタッチキャリブレーションおよびテスト

- ✓ PCIe-Gen5 Rev1.0デバイスをサポート

- ✓ 再現性の高いテスト信号キャリブレーションとRxテストを実行

## PCI Express Gen5リンクトレーニング(1/7)

#### ストレス信号 キャリブレーション

ループバック ステータスへの移行 ストレス信号 入力テスト

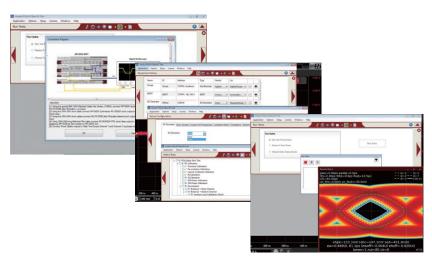

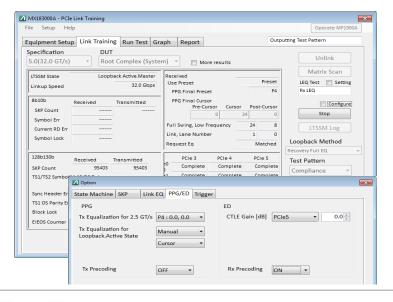

➤ MX183000A-PL025を使用したリンクトレーニング

MX183000Aを使用したPPGパターン制御

- ✓ 測定条件の設定とテストの実行を容易にする 画面機能

- ✓ PCI Expressデバイスステータスを制御し、 論理サブブロック評価をサポート

- ✓ 8B/10B、128B/130B、Scramble、

SKIP Insertion

PCI Expressリンクトレーニング画面

| 項目               | MX183000A-PL025の仕様                                                        |

|------------------|---------------------------------------------------------------------------|

| サポートする規格         | Gen5 (32 GT/s)                                                            |

| テストパターン          | Compliance (MCP、CP) 、PRBS (7、9、10、11、15、20、23、31)                         |

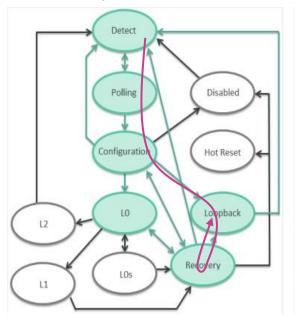

| LTSSMステート        | Detect、Polling、Configuration、Recovery、Loopbackへの遷移                        |

| Loopback Through | Configuration、Recovery                                                    |

| TS設定パターン         | SKP Insert/Filter、8B/10B、128B/130B、FTS、Link Number、Lane Number、Scrambling |

# PCI Express Gen5リンクトレーニング(2/7)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

▶ リンクトレーニングに影響を与えるいくつかのパラメータの付加および変更

| 要求事項                | 説明                                                                                       |

|---------------------|------------------------------------------------------------------------------------------|

| リンク動作制御の強化          | LEQのためのTSパラメータをPCIe 5.0に付加                                                               |

| プリコーディング            | レシーバは32.0 GT/s以上のデータレートでの運用を目的としてトランスミッタからプリコーディングをリクエストできます                             |

| SKP OS/EIEOS/EIEOSQ | SKP OS識別子をAAhから99hに変更<br>32G EIEOSは2つの16G EIEOSを連続させて32.0GT/sの<br>データレートにした場合と同じ周波数を持ちます |

| MCP 5.0             | EIEOSをEIEOSQに変更                                                                          |

# PCI Express Gen5リンクトレーニング(3/7)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

▶ リンクビヘイビア制御の強化

コンフィギュレーションルートを通じてループバックを選ぶ際のリカバリ・ イコライゼーションを目的として定義されたオプション

32 GT/sのみ (新規)

8、16および32 GT/s (レガシー)

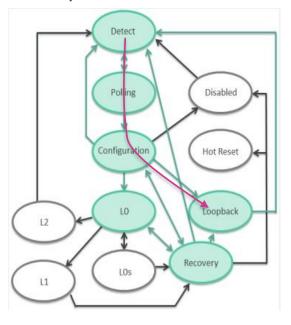

# PCI Express Gen5リンクトレーニング(4/7)

ストレス信号 キャリブレーション

ループバック ステータスへの移行 ストレス信号 入力テスト

▶ リンクビヘイビア制御の強化

リンクイコライゼーションのために定義された新規のルート

| ケース | 8.0 GT/s EQ | 16.0 GT/s EQ | 32.0 GT/s EQ | 説明                                    |

|-----|-------------|--------------|--------------|---------------------------------------|

| Α   | <b>√</b>    | -            | -            | PCIe 3                                |

| В   | ✓           | ✓            | -            | PCIe 4                                |

| С   | -           | -            | <b>√</b>     | PCIe 5イコライゼーションバイパスにより<br>最高のレートをサポート |

| D   | ✓           | ✓            | ✓            | PCIe 5の完全なイコライゼーションが必要                |

| E   | -           | -            | -            | PCIe 5のイコライゼーションは不要                   |

### PCI Express Gen5リンクトレーニング(5/7)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

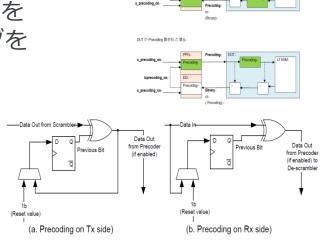

#### ▶ プリコーディング

32.0 GT/sでは、レシーバが任意で有効にできるプリコーディングメカニズムが 提供され、密かなデータ破損を引き起こす高遷移データパターンにおけるDFE 関連のエラーバーストを減らすことができます。

レシーバは32.0 GT/s以上のデータレートでの運用を 目的として、トランスミッタからプリコーディングを リクエストできます。

プリコーディングはTxまたはRxのいずれかに 個別に適用できます。

Figure 4-20 Precoding working the scrambler/de-scrambler

# PCI Express Gen5リンクトレーニング(6/7)

ストレス信号 キャリブレーション

ループバック ステータスへの移行 ストレス信号 入力テスト

- ▶ MX183000Aは下記をすでにサポート:

- ✔ 強化されたリンクビヘイビア制御

- ✓ プリコーディング

- √ SKP OS/EIEOS

- **✓** MCP 5.0

# PCI Express Gen5リンクトレーニング(7/7)

ストレス信号 キャリブレーション

ループバック ステータスへの移行 ストレス信号 入力テスト

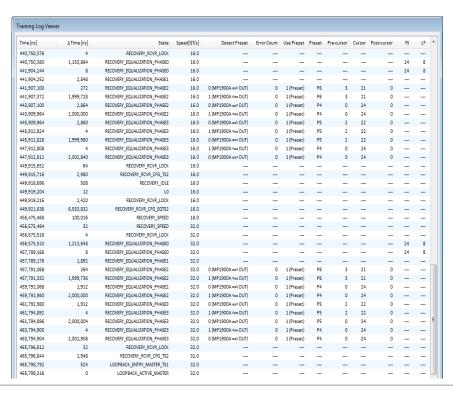

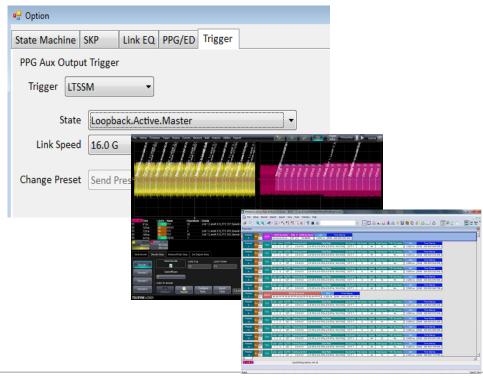

➤ MX183000Aが顧客のデバッグを確実にサポート

LTSSMログビューア

LTSSMトリガ

### PCI Express Gen5 Rx JTOLテスト(1/5)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

MX183000A - Jitter Tolerance

マージンテスト)

MX183000Aを使用したジッタ制御とトレランス測定

- ✓ SJを印可し、PHYデバイスのジッタトレランスをテスト

- ✓ 低BER推定を使用してデバイスマージンをテスト

- ✓ HTMLおよびCSVフォーマットで測定結果を 出力

| Di  | splay           | ✓.              | — Highlight I             | rror Rate | 1.0 E-                | 15 🛊            |                    |     |         |

|-----|-----------------|-----------------|---------------------------|-----------|-----------------------|-----------------|--------------------|-----|---------|

|     |                 |                 | TesterLimit<br>LowerLimit | •         | HighlightErro<br>Mask | orRate —        | Data<br>UpperLimit |     |         |

|     | Ī               | ""              |                           |           |                       |                 |                    |     |         |

| 1   | 0 <sup>3</sup>  |                 |                           |           |                       |                 |                    |     |         |

| 1   | 0 <sup>2</sup>  |                 |                           |           |                       |                 |                    |     |         |

|     | Ī               |                 |                           |           |                       |                 |                    |     |         |

| 큐 1 | o <sup>1</sup>  |                 |                           |           |                       |                 |                    |     |         |

|     | o° ‡            |                 |                           |           |                       |                 |                    |     |         |

|     | 1               |                 |                           |           |                       |                 |                    |     |         |

| 10  | ) <sup>-1</sup> |                 |                           |           |                       |                 |                    |     |         |

| 10  | <sub>2</sub> ‡  |                 |                           |           |                       |                 |                    |     |         |

|     | ,               |                 |                           |           |                       |                 |                    |     |         |

| 10  | )-3 ‡           | 10 <sup>1</sup> | 102                       | 103       | 104                   | 10 <sup>5</sup> | 106                | 107 | 108     |

|     |                 | 10              | 10                        | 10-       |                       | Frequency       |                    | 10  | /nritsu |

| 項目        | MX183000A-PL001の仕様                                 |

|-----------|----------------------------------------------------|

| ジッタ設定範囲   | MU181500Bジッタ変調源に基づくコンパイル                           |

|           | Binary、Downward Linear、Downward Log、Upward Linear、 |

| 方向検索<br>  | Upward Log、Binary + Linear                         |

| 検出        | エラーレート、エラーカウント、推定                                  |

| エラーのしきい値  | 1.0E-3から1.0E-14                                    |

| エラーレートの強調 | 9.9E-9から1.0E-20 (推定)                               |

| レポート機能    | HTMLおよびCSVフォーマットで結果を報告                             |

## PCI Express Gen5 Rx JTOLテスト(2/5)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 \_入カテスト

- ▶ 測定システムの不確実性

- 高すぎるキャリブレーション目標

• 厳しいDUT Rxマージンにより、エラーのない測定を妨げる要素が発生

BER測定システムの不確実性を排除

### PCI Express Gen5 Rx JTOLテスト (3/5)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 \_入カテスト

- ➤ CDR内蔵のオールインワン MP1900A

- SSCを使用してデータからクロックリカバリを実行し、データ/クロックライン長の差により生じるエラーを排除

- ➤ MP1900A w/ 高信号品質および高反復性

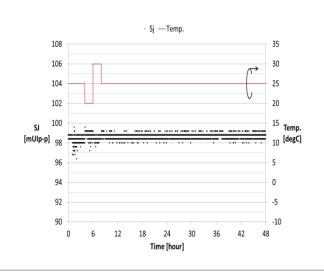

- ジッタの時間および温度への依存性:<±2%(2日間、±5°)</li>

- 低い固有ジッタ:115 fs rms

### PCI Express Gen5 Rx JTOLテスト(4/5)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

▶ クロストークが信号品質に与える影響

クロストークは高データレートで信号品質に影響を与える可能性があります。

PCIe 5 はMCPを送信するためDUTの他の非テストレーンにポートを割り当てます。 (トレーニングシーケンスシンボルナンバー5、ビット5)。

この方法では定量的なアグレッサ信号を発生させることはできません。

### PCI Express Gen5 Rx JTOLテスト(5/5)

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 \_\_入力テスト

- MP1900Aがマルチチャネルジェネレータを使用してアグレッサ信号を生成

- マルチチャネル信号ジェネレータを備えたオールインワンのBERT

- MCP送信のためのDUTリクエストをサポート

### PCI Express Gen5テストレポート

ストレス信号 キャリブレーション ループバック ステータスへの移行 ストレス信号 入力テスト

ストレス信号入力テスト

Edit/View Configuration

レポートを生成